Solid State Drive Primer # 7 - Controller Architecture - Basic Overview

![]() Previous articles described the NAND architecture from the basic NAND cell to a packaged component. This article begins to integrate the controller into the picture. Without a controller, the NAND is a relatively unintelligent storage device.

Previous articles described the NAND architecture from the basic NAND cell to a packaged component. This article begins to integrate the controller into the picture. Without a controller, the NAND is a relatively unintelligent storage device.

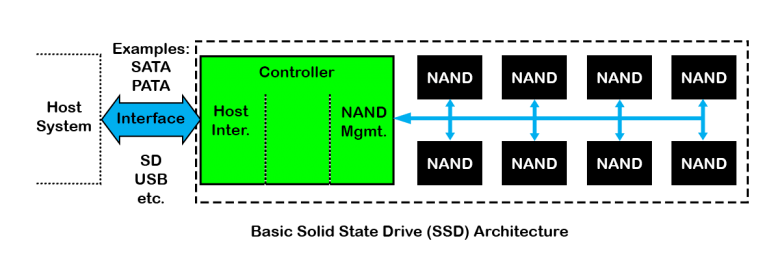

The reason for the controller function is to manage the NAND components and create a standard interface which interfaces well to host systems. There are many popular interfaces today such as Serial ATA (SATA), SD, MMC, USB, PCIe as well as Parallel ATA (PATA, aka IDE).

All of these SSD interfaces have a common controller architecture design in which a controller resides between the NAND memory and the host system. In future articles we will look at the tasks a controller handles, but here we focus on the basic architecture of a generic Solid State Drive (SSD).

As shown above, the basic SSD consists of a controller chip which manages one or more NAND components, each of which could be comprised of multiple NAND die. The diagram is generic in the sense that it doesn’t matter what final host interface is used.

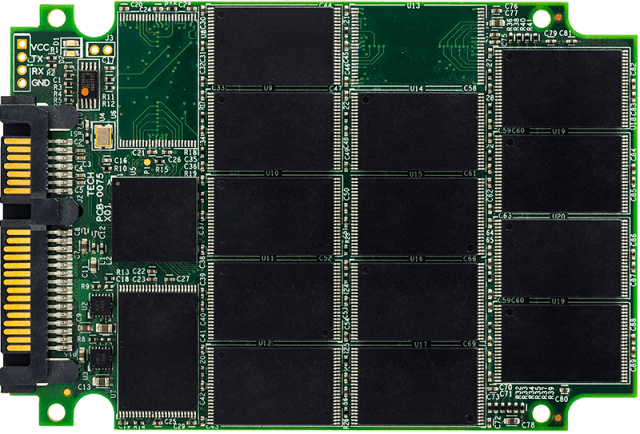

Something you’ll notice about this image is how tightly packed the NAND components are to each other. The limitation to an SSD’s storage capacity is how many NAND die can be integrated into the industry standard package along with a controller’s ability to address (read/write) each die.

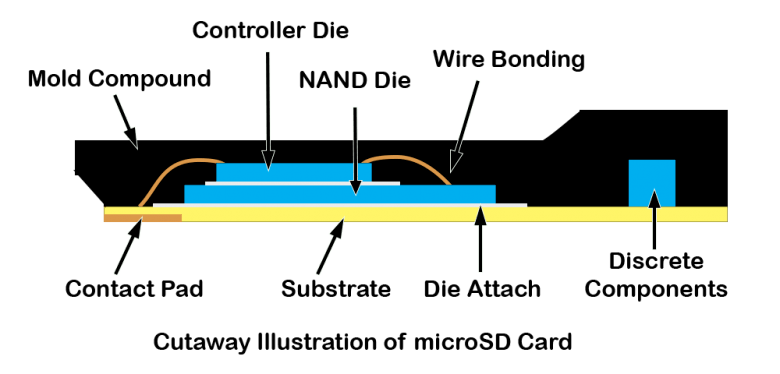

For very small packaged SSD such as microSD cards, there is not sufficient physical space for packaged NAND and controller to be used.

In these cases, the controller die and NAND die are stacked on top of each other and connections are made with wire bonding.

In these cases, the controller die and NAND die are stacked on top of each other and connections are made with wire bonding.

The diagram above only shows a single NAND die in the microSD package, but multiple NAND die can be stacked with the controller to make higher density/capacity parts. The size of the die in the cross section is not proportional to the actual size for clarity. With wafer backgrinding techniques as many 16 NAND die have been successfully integrated into a single microSD card.

The next SSD Article will focus more on multiple channels, external RAM and other features common in today’s Solid State Drive devices.

If you would like to discuss this further please contact us.

Your point of view caught my eye and was very interesting. Thanks. I have a question for you.

Your article helped me a lot, is there any more related content? Thanks! https://www.binance.com/si-LK/register?ref=V2H9AFPY

I don't think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

Your point of view caught my eye and was very interesting. Thanks. I have a question for you.

I don't think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

Can you be more specific about the content of your article? After reading it, I still have some doubts. Hope you can help me.

Thank you for your sharing. I am worried that I lack creative ideas. It is your article that makes me full of hope. Thank you. But, I have a question, can you help me?

Your article helped me a lot, is there any more related content? Thanks!

Your article helped me a lot, is there any more related content? Thanks!

Your article helped me a lot, is there any more related content? Thanks!

Your article helped me a lot, is there any more related content? Thanks!

Can you be more specific about the content of your article? After reading it, I still have some doubts. Hope you can help me.

I don't think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

Thanks for sharing. I read many of your blog posts, cool, your blog is very good.