NAND Wear Leveling a Necessity for Solid State Devices

NAND flash memory is the building block of almost every solid-state flash storage device today. A limitation of NAND flash is the number of erase cycles per block. Since erasing blocks of NAND is required prior to writing over existing data, this translates into limited write “endurance” cycles.

Current SLC NAND has a raw endurance rate of 50K-70K cycles per physical block, MLC NAND from 3K-5K and the latest TLC NAND used in consumer devices ~300 cycles.

Without a method to best use these limited NAND endurance cycles, it would be difficult to support Industrial applications with SLC NAND and Commercial applications with MLC NAND. TLC NAND would be practically unusable for any applications. [See white paper for in-depth discussion of SLC and MLC NAND.]

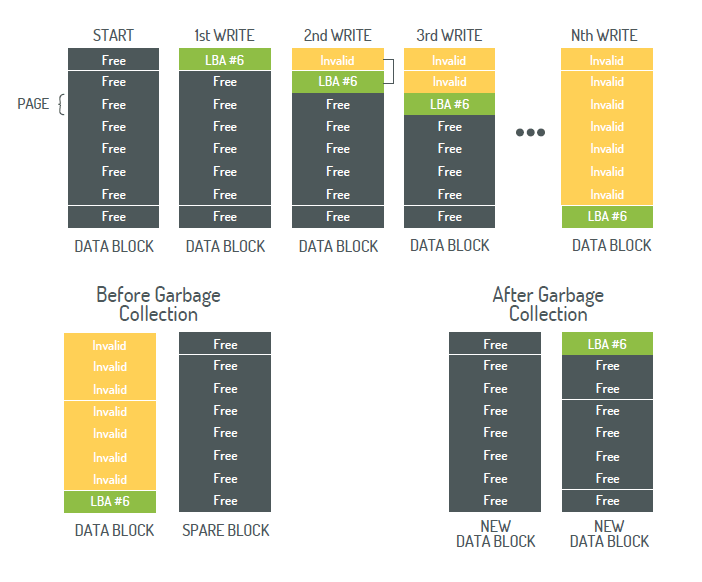

Dynamic wear leveling writes data from the host to new or previously erased blocks. For example, the host system can write continuously to one logical block, but the controller redirects each new write to a different physical block of NAND memory. This more efficiently uses all endurance cycles versus wearing out an individual NAND block.

Static wear leveling has the purpose of releasing endurance cycles from NAND blocks for data which doesn’t change. As an example, operating system files stored once and no longer modified. Since data is never modified, it could potentially use only one of up to 70K endurance cycles of a particular NAND block – at the same time other blocks completely exhaust their 70K endurance cycles.

To free up unused endurance cycles, static wear leveling moves static data to locations with a higher erase count so endurance cycles from an infrequently written block of memory can be used.

In older controllers, many wear leveling routines would group blocks by NAND component. In solid state devices with multiple NAND components, a single NAND component may exhaust its endurance cycles while many are still remaining on other NAND components.

Global wear leveling resolves this issue by using all NAND components for the wear leveling pool. This evenly uses every endurance cycle on every NAND component.

If interested in a more detailed review of wear leveling, Cactus has the following white paper for download: Wear Leveling – Static, Dynamic and Global.