# Industrial Grade CF Card -303-32 Series Product Manual

www.cactus-tech.com

The information in this manual is believed to be accurate at the time of publication but is subject to change without notice. Cactus Technologies® Limited shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or consequential damages resulting from the furnishing, performance, or use of this material.

Cactus Technologies® makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Cactus Technologies® assume any liability arising out of the application or use of its products, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

Cactus Technologies® products are not designed, intended or authorized for use as components in systems intended for surgical implant into the body or in other applications intended to support or sustain life or for any application where the failure of a Cactus Technologies® product can result in personal injury or death. Users of Cactus Technologies® products for such unintended and unauthorized applications shall assume all risk of such use and shall indemnify and hold Cactus Technologies® and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damages, expenses and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended and unauthorized use, even if such claim alleges that Cactus Technologies® was negligent regarding the design or manufacture of the part.

All parts of the Cactus Technologies® documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior consent, in writing, from Cactus Technologies®, Limited.

© 2005-2023 Cactus Technologies Limited. All rights reserved.

# **Table of Contents**

| 1.Introduction to Cactus Technologies® Industrial Grade CF -303-32 Series Products            |    |

|-----------------------------------------------------------------------------------------------|----|

| 1.1.Supported Standards                                                                       |    |

| 1.2.Product Features                                                                          |    |

| 1.2.1.Host and Technology Independence                                                        |    |

| 1.2.2.Defect and Error Management                                                             |    |

| 1.2.3.Intelligent Power Management                                                            | 3  |

| 1.2.4.Power Supply Requirements                                                               | 3  |

| 2.Product Specifications                                                                      | 1  |

| 2.1.System Environmental Specifications                                                       |    |

| 2.2.System Power Requirements                                                                 |    |

| 2.3.System Performance                                                                        |    |

| 2.4.System Reliability                                                                        |    |

| 2.5.Physical Specifications                                                                   |    |

| 2.5.1.CompactFlash Physical Specifications                                                    | 5  |

| 2.6.Capacity Specifications                                                                   | 7  |

| 3.Interface Description.                                                                      | g  |

| 3.1.CF Pin Assignments and Pin Type                                                           |    |

| 3.2.Signal Description                                                                        |    |

| 3.3.Electrical Specification                                                                  |    |

| 3.3.1.Absolute Maximum Ratings                                                                |    |

| 3.3.2.DC Characteristics                                                                      |    |

| 3.3.3.AC Characteristics.                                                                     |    |

| 3.4.Card Configuration.                                                                       |    |

| 3.4.1.Attribute Memory Function.                                                              |    |

| 3.4.2.Configuration Option Register (Address 200h in Attribute Memory)                        |    |

| 3.4.3.Card Configuration and Status Register (Address 202h in Attribute Memory)               |    |

| 3.4.4.Pin Replacement Register (Address 204h in Attribute Memory)                             |    |

|                                                                                               |    |

| 3.4.5.Socket and Copy Register (Address 206h in Attribute Memory)                             |    |

| 3.5.I/O Transfer Function                                                                     |    |

| 3.6.Common Memory Transfer Function                                                           |    |

| 5.7.11ue IDE Mode I/O Transfer Function                                                       | 10 |

| 4.ATA Drive Register Set Definition and Protocol                                              | 18 |

| 4.1.I/O Primary and Secondary Address Configurations                                          | 19 |

| 4.2.Contiguous I/O Mapped Addressing                                                          | 19 |

| 4.3.Memory Mapped Addressing                                                                  |    |

| 4.4.True IDE Mode Addressing                                                                  |    |

| 4.5.ATA Registers                                                                             |    |

| 4.5.1.Data Register (Address—1F0[170];Offset 0, 8, 9)                                         |    |

| 4.5.2.Error Register (Address—1F1[171]; Offset 1, 0Dh Read Only)                              |    |

| 4.5.3.Feature Register (Address—1F1[171]; Offset 1, 0Dh Write Only                            | 23 |

| 4.5.4.Sector Count Register (Address—1F2[172]; Offset 2)                                      |    |

| 4.5.5.Sector Number (LBA 7-0) Register (Address—1F3[173]; Offset 3)                           | 23 |

| 4.5.6.Cylinder Low (LBA 15-8) Register (Address—1F4[174]; Offset 4)                           | 23 |

| 4.5.7.Cylinder High (LBA 23-16) Register (Address—1F5[175]; Offset 5)                         |    |

| 4.5.8.Drive/Head (LBA 27-24) Register (Address 1F6[176]; Offset 6)                            |    |

| 4.5.9.Status and Alternate Status Registers (Address 1F7[177] and 3F6[376]; Offsets 7 and Eh) |    |

| 4.5.10.Device Control Register (Address—3F6[376]; Offset Eh)                                  |    |

| 4.5.11.Card (Drive) Address Register (Address 3F7[377]; Offset Eh)                            |    |

| 4.3.11. Calu (Dilve) Addiess Register (Addiess 3F/[3//], Oliset Fil)                          | ∠⊃ |

| 5.S.M.A.R.T Feature Set                                 | 25 |

|---------------------------------------------------------|----|

| 5.1.SMART Enable Operations                             |    |

| 5.2.SMART Disable Operations                            | 26 |

| 5.3.SMART Enable/Disable Attribute Autosave             | 26 |

| 5.4.SMART Read Data                                     |    |

| 5.4.1.Spare Block Count Attribute                       | 28 |

| 5.4.2.Erase Count Attribute                             | 28 |

| 5.4.3.Total ECC Error Attribute                         | 29 |

| 5.4.4.Correctable ECC Error Attribute                   | 29 |

| 5.4.5.UDMA CRC Error Attribute                          | 29 |

| 5.4.6.Total Number of Reads Attribute                   | 30 |

| 5.5.SMART Read Attribute Threshold                      | 30 |

| 5.5.1.Spare Block Count Attribute Threshold             |    |

| 5.5.2.Erase Count Attribute Threshold                   | 31 |

| 5.5.3.Total ECC Errors Attribute Threshold              | 31 |

| 5.5.4.Correctable ECC Errors Attribute Threshold        | 31 |

| 5.5.5.UDMA CRC Errors Attribute Threshold               | 31 |

| 5.5.6.Total Number of Reads Attribute Threshold         | 31 |

| 5.6.SMART Return Status                                 | 32 |

|                                                         |    |

| 6.CIS Description                                       | 33 |

| Appendix A.Ordering Information                         | 43 |

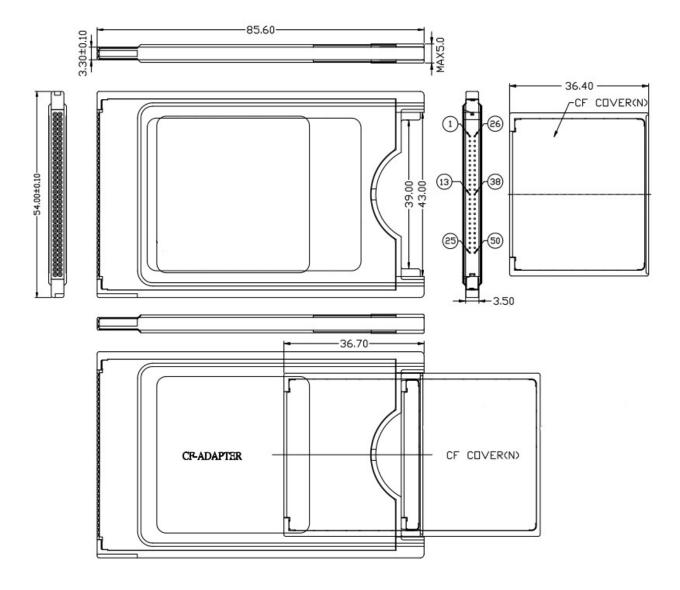

| Appendix B.CF To PC Card Adapter Information            | 44 |

| rippendix 5.01 1010 Outd riduplet information           |    |

| Appendix C.Technical Support Services                   | 45 |

| Appendix D.Cactus Technologies® Worldwide Sales Offices | 46 |

|                                                         |    |

| Appendix F. Limited Warranty                            | 47 |

1.Introduction to Cactus Technologies® Industrial Grade CF -303-32 Series Products

## **Features:**

- Solid state design with no moving parts

- Industry standard CF Type I form factor

- Supports TrueIDE Mode

- Supports ATA PIO Modes 0-6 in TrueIDE Mode

- Supports MultiWord DMA Modes 0-4 in TrueIDE Mode

- Supports UDMA Modes 0-4 in TrueIDE Mode

- Supports ATA S.M.A.R.T. Feature Set

- High reliability, MTBF > 4,000,000 hrs.

- Enhanced error correction, < 1 error in 10<sup>14</sup> bits read

- Intelligent power management to reduce power consumption

- Dual voltage support: 3.3V/5.0V

## Overview:

Cactus Technologies® CompactFlash® Memory Card (CF) is a high capacity solid-state flash memory product that complies with the Personal Computer Memory Card International Association (PCMCIA) ATA (PC Card ATA) standard. It also supports True IDE Mode, which is electrically compatible with an IDE disk drive. CompactFlash Memory Cards provide up to 16GB of formatted storage capacity in the CF Type I form factor.

Cactus Technologies® Industrial Grade CF products use high quality flash memory from Kioxia Corporation. In addition, it includes an on-card intelligent controller that manages interface protocols, data storage and retrieval as well as ECC, defect handling and diagnostics, power management, and clock control.

# 1.1. Supported Standards

Cactus Technologies® CompactFlash Memory Cards are fully electrically compatible with the following specifications:

- PCMCIA PC Card Standard v2.1

- PCMCIA PC Card ATA Specification

- CompactFlash Specification 3.0

- ATA Specification published by ANSI: X3.221 AT Attachment Interface for Disk Drives

## 1.2. Product Features

Cactus Technologies® Industrial Compact Flash Cards contain a high level, intelligent controller. This intelligent controller provides many capabilities not found in other types of memory cards. These capabilities include the following:

- Standard ATA register and command set (same as found on most magnetic disk drives).

- Manages details of erasing and programming flash memory independent of the host system

- Sophisticated defect managing capabilities (similar to magnetic disk drives).

- Sophisticated system for error recovery using powerful error correction code (ECC).

- Intelligent power management for low power operation.

# **1.2.1.** Host and Technology Independence

Cactus Technologies® Industrial CF Cards appears as a standard ATA disk drive to the host system. The card utilizes a 512-byte sector which is the same as that in an IDE magnetic disk drive. To write or read a sector (or multiple sectors), the host computer software simply issues an ATA Read or Write command to the card as per the ATA protocol. The host software then waits for the command to complete. The host system does not get involved in the details of how the flash memory is erased, programmed or read as this is all managed by the built-in controller in the card. Also, with the intelligent on-board controller, the host system software will not require changing as new flash memory evolves. Thus, systems that support the Cactus Technologies® Industrial CF products today will continue to work with future Cactus Technologies® Industrial CF cards built with new flash technology without having to update or change host software.

## **1.2.2.** Defect and Error Management

Cactus Technologies® Industrial CF cards contain a sophisticated defect and error management system similar to those found in magnetic disk drives. The defect management is completely transparent to the host and does not consume any user data space.

The soft error rate for Cactus Technologies® Industrial CF cards is much lower than that of magnetic disk drives. In the extremely rare case where a read error does occur, the card has sophisticated ECC to recover the data.

These defect and error management systems, coupled with the solid-state construction, give Cactus Technologies® Industrial CF cards unparalleled reliability.

## 1.2.3. Intelligent Power Management

Cactus Technologies® Industrial CF cards employ sophisticated power management algorithms to conserve power. Upon completion of a command, the card will automatically enter sleep mode if no further commands are received. In most situations, the card will be in sleep mode except when the host is accessing it, thus conserving power. The delay from command completion to entering sleep mode can be adjusted.

When the card is in sleep mode, any command issued to the card will cause it to exit sleep and respond.

## 1.2.4. Power Supply Requirements

This is a dual voltage product, which means it will operate at a voltage range of 3.30 volts  $\pm 5\%$  or 5.00 volts  $\pm 10\%$ . Per the PCMCIA specification Section 2.1.1, the host system must apply 0 volts in order to change a voltage range. This same procedure of providing 0 volts to the card is required if the host system applies an input voltage outside the desired voltage by more than 20%. This means less than 4.0 volts for the 5.00 volt range and less than 2.70 volts for the 3.30 volt range.

# 2. Product Specifications

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

# 2.1. System Environmental Specifications

**Table 2-1. Environmental Specifications**

|                                  |                                | Cactus Technologies® CF<br>Products                      |

|----------------------------------|--------------------------------|----------------------------------------------------------|

| Temperature                      | Operating:                     | 0° C to +70° C (Standard)<br>-40° C to +85° C (Extended) |

| Humidity                         | Operating & Non-<br>Operating: | 8% to 95%, non-condensing                                |

| Acoustic Noise                   |                                | 0 dB                                                     |

| Vibration                        | Operating & Non-<br>Operating: | 30 G peak to peak maximum                                |

| Shock                            | Operating & Non-<br>Operating: | 3,000 G maximum                                          |

| Altitude (relative to sea level) | Operating & Non-<br>Operating: | 100,000 feet maximum                                     |

# 2.2. System Power Requirements

**Table 2-2. Power Requirements**

|                                                          |                               | Cactus Technologies® Industrial CF Products |                          |  |  |

|----------------------------------------------------------|-------------------------------|---------------------------------------------|--------------------------|--|--|

| DC Input Voltage<br>(VCC)<br>100 mV max. ripple<br>(p-p) |                               | 5.0V ±10%                                   | 3.3V ±5%                 |  |  |

| (Maximum Average<br>Value)<br>See Notes.                 |                               |                                             |                          |  |  |

| 1GB or lower capacities                                  | Idle:<br>Reading:<br>Writing: | 2 mA<br>95 mA<br>85 mA                      | 2 mA<br>110 mA<br>100 mA |  |  |

| 2GB or higher capacities                                 | Idle:<br>Reading:             | 2 mA<br>170mA                               | 2 mA<br>200mA            |  |  |

|                                                          | Writing:                      | 155mA                                       | 175mA                    |  |  |

\_\_\_\_

**NOTES**: All values quoted are typical at ambient temperature and nominal supply voltage unless otherwise stated.

Sleep mode is specified under the condition that all card inputs are static CMOS levels and in a "Not Busy" operating state.

# 2.3. System Performance

All performance numbers are typical values assuming the card controller is in the default (i.e., fastest) mode.

Table 2-3. Performance

| Read Transfer Rate  | up to 35.0 Mbytes/sec * |

|---------------------|-------------------------|

| Write Transfer Rate | up to 25.0 Mbytes/sec * |

<sup>\*</sup> Please note that for maximum performance in TrueIDE UDMA modes, proper termination and PCB layout guidelines as described in the ATA specifications must be followed to minimize signal integrity problems. Maximum transfer rates are achieved on 2GB or higher capacity cards.

2.4. System Reliability

**Table 2-4. Reliability**

| Data Reliability | < 1 non-recoverable error in 10 <sup>14</sup> bits READ |

|------------------|---------------------------------------------------------|

| Endurance:       | Estimated TBW                                           |

| 128MB            | 8.75TB                                                  |

| 256MB            | 17.5TB                                                  |

| 512MB            | 35TB                                                    |

| 1GB              | 70TB                                                    |

| 2GB              | 140TB                                                   |

| 4GB              | 280TB                                                   |

| 8GB              | 560TB                                                   |

| 16GB             | 1120TB                                                  |

Note: Estimated TBW is based on a workload of large, sequential blocks. A workload of random, small blocks will result in significantly lower TBW. Estimated TBW does not take into account data retention.

## 2.5. Physical Specifications

The following sections provide the physical specifications for Cactus Technologies® Industrial CompactFlash products.

## 2.5.1. CompactFlash Physical Specifications

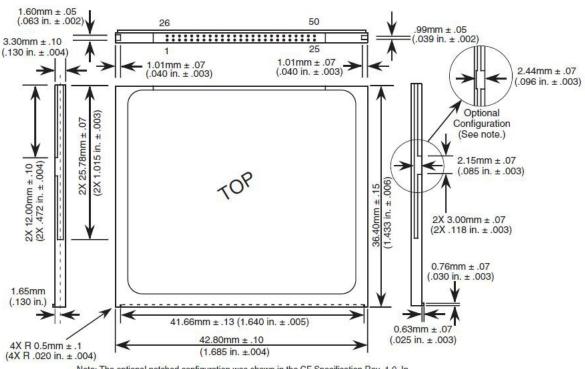

Refer to Table 2-5 and see Figure 2-1 for CompactFlash Memory Card physical specifications and dimensions.

**Table 2-5. CompactFlash Physical Specifications**

| Weight:    | 11.4 g (.40 oz) typical, 14.2 g (.50 oz) maximum |

|------------|--------------------------------------------------|

| Length:    | 36.40 ± 0.15 mm (1.433 ±.006 in)                 |

| Width:     | 42.80 ± 0.10 mm (1.685 ±.004 in)                 |

| Thickness: | 3.3 mm ± 0.10 mm (.130 ±.004 in) (Excluding Lip) |

Figure 2-1. CompactFlash Memory Card Dimensions

Note: The optional notched configuration was shown in the CF Specification Rev. 1.0. In specification Rev. 1.2, the notch was removed for ease of tooling. This optional configuration can be used but it is not recommended.

# 2.6. Capacity Specifications

Cactus Technologies® offers CompactFlash products in the following capacities:

128M, 256M, 512M, 1G, 2G, 4G, 8G and 16G

# **3.Interface Description**

The following sections provide detailed information on the Cactus Technologies® Industrial CompactFlash card interface.

# 3.1. CF Pin Assignments and Pin Type

The signal/pin assignments are listed in Table 3-6. Low active signals have a "-" prefix. Pin types are Input, Output or Input/Output. Sections 3.3.1 to 3.3.4 define the DC characteristics for all input and output type structures.

Table 3-6. CompactFlash Pin Assignments and Pin Type

| PC Ca      | rd Memory Mode PC Card I/O Mode |                 | Т          | rue IDE Mode      |                 |            |                       |             |

|------------|---------------------------------|-----------------|------------|-------------------|-----------------|------------|-----------------------|-------------|

| Pin<br>Num | Signal<br>Name                  | Pin<br>Ty<br>pe | Pin<br>Num | Signal<br>Name    | Pin<br>Typ<br>e | Pin<br>Num | Signal<br>Name        | Pin<br>Type |

| 1          | GND                             |                 | 1          | GND               |                 | 1          | GND                   |             |

| 2          | D03                             | I/O             | 2          | D03               | I/O             | 2          | D03                   | I/O         |

| 3          | D04                             | I/O             | 3          | D04               | I/O             | 3          | D04                   | I/O         |

| 4          | D05                             | I/O             | 4          | D05               | I/O             | 4          | D05                   | I/O         |

| 5          | D06                             | I/O             | 5          | D06               | 1/0             | 5          | D06                   | I/O         |

| 6          | D07                             | I/O             | 6          | D07               | I/O             | 6          | D07                   | I/O         |

| 7          | -CE1                            | -               | 7          | -CE1              | -               | 7          | -CS0                  | I           |

| 8          | A10                             | 1               | 8          | A10               | - 1             | 8          | A10 <sup>2</sup>      | 1           |

| 9          | -OE                             | -               | 9          | -OE               | -               | 9          | -ATA SEL              | 1           |

| 10         | A09                             | I               | 10         | A09               | ı               | 10         | A09 <sup>2</sup>      | I           |

| 11         | A08                             | I               | 11         | A08               | I               | 11         | A08 <sup>2</sup>      | I           |

| 12         | A07                             | -               | 12         | A07               | -               | 12         | A07 <sup>2</sup>      | 1           |

| 13         | VCC                             |                 | 13         | VCC               |                 | 13         | VCC                   |             |

| 14         | A06                             | ı               | 14         | A06               | 1               | 14         | A06 <sup>2</sup>      | I           |

| 15         | A05                             | ı               | 15         | A05               | ı               | 15         | A05 <sup>2</sup>      | I           |

| 16         | A04                             | ı               | 16         | A04               | 1               | 16         | A04 <sup>2</sup>      | I           |

| 17         | A03                             | ı               | 17         | A03               | ı               | 17         | A03 <sup>2</sup>      | I           |

| 18         | A02                             | ı               | 18         | A02               | 1               | 18         | A02                   | I           |

| 19         | A01                             | 1               | 19         | A01               | - 1             | 19         | A01                   | 1           |

| 20         | A00                             | -               | 20         | A00               | -               | 20         | A00                   | I           |

| 21         | D00                             | I/O             | 21         | D00               | I/O             | 21         | D00                   | I/O         |

| 22         | D01                             | I/O             | 22         | D01               | I/O             | 22         | D01                   | I/O         |

| 23         | D02                             | I/O             | 23         | D02               | I/O             | 23         | D02                   | I/O         |

| 24         | WP                              | 0               | 24         | -IOIS16           | 0               | 24         | -IOCS16               | 0           |

| 25         | -CD2                            | 0               | 25         | -CD2              | 0               | 25         | -CD2                  | 0           |

| 26         | -CD1                            | 0               | 26         | -CD1              | 0               | 26         | -CD1                  | 0           |

| 27         | D11 <sup>1</sup>                | I/O             | 27         | D11 <sup>1</sup>  | I/O             | 27         | D11 <sup>1</sup>      | I/O         |

| 28         | D12 <sup>1</sup>                | I/O             | 28         | D12 <sup>1</sup>  | I/O             | 28         | D12 <sup>1</sup>      | I/O         |

| 29         | D13 <sup>1</sup>                | 1/0             | 29         | D13 <sup>1</sup>  | 1/0             | 29         | D13 <sup>1</sup>      | I/O         |

| 30         | D14 <sup>1</sup>                | I/O             | 30         | D14 <sup>1</sup>  | I/O             | 30         | D14 <sup>1</sup>      | I/O         |

| 31         | D15 <sup>1</sup>                | I/O             | 31         | D15 <sup>1</sup>  | I/O             | 31         | D15 <sup>1</sup>      | I/O         |

| 32         | -CE2 <sup>1</sup>               | ı               | 32         | -CE2 <sup>1</sup> | ı               | 32         | -CS1 <sup>1</sup>     | ı           |

| 33         | -VS1                            | 0               | 33         | -VS1              | 0               | 33         | -VS1                  | 0           |

|            | -IORD                           |                 |            | -IORD             |                 |            | -IORD                 |             |

| 34         |                                 | 1               | 34         |                   | 1               | 34         | HSTROBE <sup>5</sup>  | ı           |

|            |                                 |                 |            |                   |                 |            | -HDMARDY <sup>6</sup> |             |

| 05         | 101415                          |                 | 05         | IOME              |                 | 05         | -IOWR                 |             |

| 35         | -IOWR                           | I               | 35         | -IOWR             | I               | 35         | STOP <sup>7</sup>     | I           |

| 36         | -WE                             | I               | 36         | -WE               | I               | 36         | -WE <sup>3</sup>      | ı           |

8

| PC Ca | PC Card Memory Mode |     |    | PC Card I/O Mode |     | Т  | rue IDE Mode         |     |

|-------|---------------------|-----|----|------------------|-----|----|----------------------|-----|

| 37    | RDY/BSY             | 0   | 37 | IREQ             | 0   | 37 | INTRQ                | 0   |

| 38    | VCC                 |     | 38 | VCC              |     | 38 | VCC                  |     |

| 39    | -CSEL               | - 1 | 39 | -CSEL            | 1   | 39 | -CSEL                | I   |

| 40    | -VS2                | 0   | 40 | -VS2             | 0   | 40 | -VS2                 | 0   |

| 41    | RESET               | - 1 | 41 | RESET            | 1   | 41 | -RESET               | I   |

|       |                     |     |    |                  |     |    | IORDY                |     |

| 42    | -WAIT               | 0   | 42 | -WAIT            | 0   | 42 | -DDMARDY⁵            | 0   |

|       |                     |     |    |                  |     |    | DSTROBE <sup>6</sup> |     |

| 43    | -INPACK             | 0   | 43 | -INPACK          | 0   | 43 | DMARQ                | 0   |

| 44    | -REG                | - 1 | 44 | -REG             | I   | 44 | -DMACK               | I   |

| 45    | BVD2                | I/O | 45 | -SPKR            | I/O | 45 | -DASP                | I/O |

| 46    | BVD1                | I/O | 46 | -STSCHG          | I/O | 46 | -PDIAG               | I/O |

| 47    | D08 <sup>1</sup>    | I/O | 47 | D08 <sup>1</sup> | I/O | 47 | D08 <sup>1</sup>     | I/O |

| 48    | D09 <sup>1</sup>    | I/O | 48 | D09 <sup>1</sup> | I/O | 48 | D09 <sup>1</sup>     | I/O |

| 49    | D10 <sup>1</sup>    | I/O | 49 | D10 <sup>1</sup> | I/O | 49 | D10 <sup>1</sup>     | I/O |

| 50    | GND                 |     | 50 | GND              |     | 50 | GND                  |     |

#### NOTE:

- 1. These signals are required only for 16-bit access and not required when installed in 8-bit systems. For lowest power dissipation, leave these signals open.

- 2. Should be grounded by the host.

- 3. Should be tied to VCC by the host.

- 4. Please refer to Section 3.3 for definitions of In, Out type.

- 5. Signal usage when UDMA write protocol is active.

- 6. Signal usage when UDMA read protocol is active.

- 7. Signal usage when UDMA protocol is active.

## 3.2. Signal Description

Cactus Technologies® Industrial CompactFlash products can be configured to operate in either I/O mode or memory mode as per the *PCMCIA Release 2.1 specification*. The configuration of the CompactFlash cards are controlled using the standard PCMCIA configuration registers starting at address 200h in the Attribute Memory space of the CompactFlash Memory Card. Cactus Technologies® Industrial CompactFlash cards also supports a TrueIDE mode. This mode is entered by grounding the –OE pin on power up.

Table 3-7 describes the I/O signals. Signals whose source is the host are designated as inputs while signals that the CompactFlash Memory Card sources are outputs. The CompactFlash Card logic levels conform to those specified in the *PCMCIA Release 2.1 Specification*. See Section 3.3 for definitions of Input and Output type.

| Table : | 3-7. | Signal | Descri | ption |

|---------|------|--------|--------|-------|

|---------|------|--------|--------|-------|

| Signal Name                                           | Dir. | Description                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10—A0<br>(CF Card Memory<br>Mode)                    | ı    | These address lines along with the -REG signal are used to select the following: The I/O port address registers within the CompactFlash Card, the memory mapped port address registers within the card, a byte in the card's information structure and its configuration control and status registers. |

| A10—A0<br>(CF Card I/O Mode)                          |      | This signal is the same as the CF Card Memory Mode signal.                                                                                                                                                                                                                                             |

| A2—A0<br>(True IDE Mode)<br>A10—A3<br>(True IDE Mode) | I    | In True IDE Mode only A[2:0] is used to select the one of eight registers in the Task File.  In True IDE Mode these remaining address lines should be grounded by the host.                                                                                                                            |

| BVD1<br>(CF Card Memory<br>Mode)                      | I/O  | This signal is asserted high as the BVD1 signal since a battery is not used with this product.                                                                                                                                                                                                         |

| Signal Name                                           | Dir. | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -STSCHG                                               | DII. | This signal is asserted low to alert the host to changes in the RDY/-BSY and Write Protect                                                                                                                                                                                                                                                                                                                  |

| (CF Card I/O Mode)<br>Status Changed                  |      | states, while the I/O interface is configured. Its use is controlled by the Card Config and Status Register.                                                                                                                                                                                                                                                                                                |

| -PDIAG<br>(True IDE Mode)                             |      | In the True IDE Mode, this input/output is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                                                                               |

| BVD2<br>(CF Card Memory<br>Mode)                      | I/O  | This output line is always driven to a high state in Memory Mode since a battery is not required for this product.                                                                                                                                                                                                                                                                                          |

| -SPKR<br>(CF Card I/O Mode)                           |      | This output line is always driven to a high state in I/O Mode since this product does not support the audio function.                                                                                                                                                                                                                                                                                       |

| -DASP<br>(True IDE Mode)                              |      | In the True IDE Mode, this input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                                                                     |

| -CD1, -CD2<br>(CF Card Memory<br>Mode)                | 0    | These Card Detect pins are connected to ground on the CompactFlash Card. They are used by the host to determine if the card is fully inserted into its socket.                                                                                                                                                                                                                                              |

| -CD1, -CD2<br>(CF Card I/O Mode)                      |      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                      |

| -CD1, -CD2<br>(True IDE Mode)                         |      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                      |

| -CE1, -CE2<br>(CF Card Memory<br>Mode)<br>Card Enable | l    | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performedCE2 always accesses the odd byte of the wordCE1 accesses the even byte or the Odd byte of the word depending on A0 and -CE2. A multiplexing scheme based on A0, -CE1, and -CE2 allows 8 bit hosts to access all data on D0-D7. See Tables 3-11, 3-12, 3-15, and 3-16. |

| -CE1, -CE2<br>(CF Card I/O Mode)<br>Card Enable       |      | This signal is the same as the CF Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                  |

| -CS0, -CS1<br>(True IDE Mode)                         |      | In the True IDE Mode -CS0 is the chip select for the task file registers while -CS1 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                                                                                                                        |

| -CSEL<br>(CF Card Memory<br>Mode)                     | I    | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                                                      |

| -CSEL<br>(CF Card I/O Mode)                           |      | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                                                                      |

| -CSEL<br>(True IDE Mode)                              |      | This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.                                                                                                                                                |

| D15—D00<br>(CF Card Memory<br>Mode)                   | I/O  | These lines carry the Data, Commands and Status information between the host and the controller. D00 is the LSB of the Even Byte of the Word. D08 is the LSB of the Odd Byte of the Word.                                                                                                                                                                                                                   |

| D15—D00<br>(CF Card I/O Mode)                         |      | These signals are the same as the CF Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                               |

| D15—D00<br>(True IDE Mode)                            |      | In True IDE Mode all Task File operations occur in byte mode on the low order bus D00-D07 while all data transfers are 16 bits using D00-D15.                                                                                                                                                                                                                                                               |

| GND<br>(CF Card Memory<br>Mode)                       |      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND<br>(CF Card I/O Mode)                             |      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                      |

| GND<br>(True IDE Mode)                                |      | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                      |

| -INPACK<br>(CF Card Memory<br>Mode)                   | 0    | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                       |

| -INPACK<br>(CF Card I/O Mode)<br>Input Acknowledge    |      | The Input Acknowledge signal is asserted by the CompactFlash Card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used by the host to control the enable of any input data buffers between the card and the CPU.                                                                                                                    |

| DMARQ (True IDE<br>Mode)                              |      | In True IDE Mode, this pin is an output from the card to request DMA mode transfer.                                                                                                                                                                                                                                                                                                                         |

| Signal Name                                                 | Dir. | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IORD<br>(CF Card Memory<br>Mode)                           | I    | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                         |

| -IORD<br>(CF Card I/O Mode)                                 |      | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the CompactFlash Card when the card is configured to use the I/O interface.                                                                                                                                                                                                                                                    |

| -IORD<br>(True IDE Mode, UDMA<br>not active)                |      | In True IDE Mode, when UDMA protocol is not active, this signal has the same function as in CF Card I/O Mode.                                                                                                                                                                                                                                                                                                                 |

| -HDMARDY<br>(TrueIDE Mode, UDMA read)                       |      | In TrueIDE Mode, when UDMA read protocol is active, this signal is asserted by the host to indicate that it is ready to receive data-in bursts.                                                                                                                                                                                                                                                                               |

| HSTROBE<br>(TrueIDE Mode, UDMA<br>write)                    |      | In TrueIDE Mode, when UDMA write protocol is active, this signal is the data out strobe sent by the host. Data is latched by the device on both rising and falling edges of this signal.                                                                                                                                                                                                                                      |

| -IOWR<br>(CF Card Memory<br>Mode)                           | I    | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                         |

| -IOWR<br>(CF Card I/O Mode)                                 |      | The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into the CompactFlash controller registers when the card is configured to use the I/O interface.                                                                                                                                                                                                                                                    |

| LOVACE                                                      |      | The clocking will occur on the negative to positive edge of the signal (trailing edge).                                                                                                                                                                                                                                                                                                                                       |

| -IOWR<br>(True IDE Mode, UDMA<br>not active)                |      | In True IDE Mode, when UDMA protocol is not active, this signal has the same function as in CF Card I/O Mode.                                                                                                                                                                                                                                                                                                                 |

| STOP<br>(TrueIDE Mode, UDMA active)                         |      | In TrueIDE Mode, when UDMA protocol is active, host asserts this signal to terminate the UDMA transfer.                                                                                                                                                                                                                                                                                                                       |

| -OE<br>(CF Card Memory<br>Mode)                             | I    | This is an Output Enable strobe generated by the host interface. It is used to read data from the CompactFlash Card in Memory Mode and to read the CIS and configuration registers.                                                                                                                                                                                                                                           |

| -OE<br>(CF Card I/O Mode)                                   |      | In CF Card I/O Mode, this signal is used to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                         |

| -ATA SEL<br>(True IDE Mode)                                 |      | To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                                            |

| RDY/-BSY<br>(CF Card Memory<br>Mode)                        | 0    | In Memory Mode this signal is set high when the CompactFlash Card is ready to accept a new data transfer operation and held low when the card is busy. The Host memory card socket must provide a pull-up resistor.                                                                                                                                                                                                           |

|                                                             |      | At power up and at Reset, the RDY/-BSY signal is held low (busy) until the CompactFlash Card has completed its power up or reset function. No access of any type should be made to the CompactFlash Card during this time. The RDY/-BSY signal is held high (disabled from being busy) whenever the following condition is true: The CompactFlash Card has been powered up with +RESET continuously disconnected or asserted. |

| -IREQ<br>(CF Card I/O Mode)                                 |      | I/O Operation—After the CompactFlash Card has been configured for I/O operation, this signal is used as -Interrupt Request. This line is strobed low to generate a pulse mode interrupt or held low for a level mode interrupt.                                                                                                                                                                                               |

| INTRQ<br>(True IDE Mode)                                    |      | In True IDE Mode, this signal is the active high Interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                               |

| -REG<br>(CF Card Memory<br>Mode)<br>Attribute Memory Select | I    | This signal is used during Memory Cycles to distinguish between Common Memory and Register (Attribute) Memory accesses. High for Common Memory, Low for Attribute Memory.                                                                                                                                                                                                                                                     |

| -REG<br>(CF Card I/O Mode)                                  |      | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.                                                                                                                                                                                                                                                                                                                                    |

| -DMACK (True IDE Mode)                                      |      | In True IDE Mode, this is an input from the host to signal that the DMA request from the device has been acknowledged.                                                                                                                                                                                                                                                                                                        |

| RESET<br>(CF Card Memory<br>Mode)                           | I    | When the pin is high, this signal resets the CompactFlash Card. The card is Reset only at power up if this pin is left high or open from power-up. The card is also reset when the Soft Reset bit in the Card Configuration Option Register is set.                                                                                                                                                                           |

| RESET<br>(CF Card I/O Mode)                                 |      | This signal is the same as the CF Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                    |

| Signal Name                                      | Dir. | Description                                                                                                                                                                                                                                               |

|--------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -RESET<br>(True IDE Mode)                        |      | In the True IDE Mode this input pin is the active low hardware reset from the host.                                                                                                                                                                       |

| VCC<br>(CF Card Memory<br>Mode)                  |      | +5 V, +3.3 V power.                                                                                                                                                                                                                                       |

| VCC<br>(CF Card I/O Mode)                        |      | This signal is the same for all modes.                                                                                                                                                                                                                    |

| VCC<br>(True IDE Mode)                           |      | This signal is the same for all modes.                                                                                                                                                                                                                    |

| -VS1<br>-VS2<br>(CF Card Memory<br>Mode)         | 0    | Voltage Sense SignalsVS1 is grounded so that the CompactFlash Card CIS can be read at 3.3 volts and -VS2 is open and reserved by CF Card for a secondary voltage.                                                                                         |

| -VS1<br>-VS2<br>(CF Card I/O Mode)               |      | This signal is the same for all modes.                                                                                                                                                                                                                    |

| -VS1<br>-VS2<br>(True IDE Mode)                  |      | This signal is the same for all modes.                                                                                                                                                                                                                    |

| -WAIT<br>(CF Card Memory<br>Mode)                | 0    | The –WAIT signal is driven by the CompactFlash Card to signal to the host to delay completion of the memory cycle in progress.                                                                                                                            |

| -WAIT<br>(CF Card I/O Mode)                      |      | The –WAIT signal is driven by the CompactFlash Card to signal to the host to delay completion of the I/O cycle in progress.                                                                                                                               |

| -IORDY<br>(True IDE Mode, UDMA<br>not active)    |      | In TrueIDE Mode, when UDMA protocol is not active, this signal is driven by the device to extend the I/O cycle in progress.                                                                                                                               |

| -DDMARDY<br>(TrueIDE Mode, UDMA<br>write active) |      | In TrueIDE Mode, when UDMA write protocol is active, this signal is asserted by the device to indicate that it is ready to receive a data out burst.                                                                                                      |

| DSTROBE<br>(TrueIDE Mode, UDMA<br>read active)   |      | In TrueIDE Mode, when UDMA read protocol is active, this signal is the data strobe sent by the device to the host. The host latches data on both the rising and falling edges of this signal.                                                             |

| -WE<br>(CF Card Memory<br>Mode)                  | I    | This is a signal driven by the host and used for strobing memory write data to the registers of the CompactFlash Card when the card is configured in the memory interface mode. It is also used for writing the configuration registers.                  |

| -WE<br>(CF Card I/O Mode)                        |      | In CF Card I/O Mode, this signal is used for writing the configuration registers.                                                                                                                                                                         |

| Reserved<br>(True IDE Mode)                      |      | In True IDE Mode this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                |

| WP<br>(CF Card Memory<br>Mode)<br>Write Protect  | 0    | Memory Mode—The CompactFlash Card does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.                                                                                                |

| -IOIS16<br>(CF Card I/O Mode)                    |      | I/O Operation—When the CompactFlash Card is configured for I/O Operation, Pin 24 is used for the -I/O Selected is 16 Bit Port (-IOIS16) function. A Low signal indicates that a 16 bit or odd byte only operation can be performed at the addressed port. |

| -IOCS16<br>(True IDE Mode)                       |      | In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                             |

# 3.3. Electrical Specification

The following table defines all D.C. Characteristics for the CompactFlash Memory Card Series. Unless otherwise stated, conditions are:

$$Vcc = 5V \pm 10\%$$

or  $Vcc = 3.3V \pm 5\%$

Ta = -40°C to 85°C

#### **Absolute Maximum Ratings** 3.3.1.

| Parameter               | Symbol | MIN  | MAX | Units |

|-------------------------|--------|------|-----|-------|

| Storage Temperature     | Ts     | -55  | 100 | °C    |

| Operating Temperature   | TA     | -40  | 85  | °C    |

| Vcc with respect to GND | Vcc    | -0.3 | 6.5 | V     |

#### 3.3.2. **DC Characteristics**

Cactus Technolgies® CF Cards require Power Mode 1 for both read and write operations.

| Parameter                      | Symbol                         | MIN  | MAX       | Units | Notes                                           |

|--------------------------------|--------------------------------|------|-----------|-------|-------------------------------------------------|

| Input High Voltage             | V <sub>IH</sub>                | 2.0  | Vcc + 0.3 | V     |                                                 |

| Input Low Voltage              | V <sub>IL</sub>                | -0.3 | 0.8       | V     |                                                 |

| Output Low Voltage             | V <sub>OL</sub>                |      | 0.45      | V     | At I <sub>oL</sub> of 4mA<br>(12mA for<br>DASP) |

| Output High Voltage            | $V_{OH}$                       | 2.4  |           | V     | At I <sub>OH</sub> of 1mA                       |

| Input Leakage Current          | Iu                             | -10  | 10        | uA    | Without internal pullup/pulldown                |

| Output Leakage Current         | I <sub>LO</sub>                | -10  | 10        | uA    |                                                 |

| Input/Output Capacitance       | C <sub>I</sub> /C <sub>o</sub> |      | 10        | рF    |                                                 |

| Operating Current (5V)         | Icc                            |      |           | mA    |                                                 |

| Idle                           |                                |      | 2         |       |                                                 |

| Active                         |                                |      | 0.5       |       |                                                 |

| 1GB or below:<br>2GB or above: |                                |      | 95<br>170 |       |                                                 |

#### 3.3.3. **AC Characteristics**

Cactus Technolgies® CF Cards meet all the timing requirements as specified in CompactFlash Specification 3.0 and PCMCIA PC Card Standard v2.1. Please refer to those documents for details on interface AC timing diagrams and specifications.

# 3.4. Card Configuration

CompactFlash Memory Cards are identified by information in the Card Information Structure (CIS). The entries in Table 3-8 and Table 3-9 show how to access the various registers and address spaces in the memory cards.

Table 3-8. Registers and Memory Space Decoding

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | А3 | A2 | A1 | Α0 | SELECTED SPACE                     |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|------------------------------------|

| 1    | 1    | Х    | Х   | Χ   | Х   | Х  | XX    | Х  | Х  | Х  | Х  | Standby                            |

| Х    | 0    | 0    | 0   | 1   | Х   | 1  | XX    | Х  | Х  | Х  | 0  | Configuration Registers Read       |

| 1    | 0    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х  | Х  | Χ  | Common Memory Read (8 Bit D7-D0)   |

| 0    | 1    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х  | Х  | Х  | Common Memory Read (8 Bit D15-D8)  |

| 0    | 0    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х  | Х  | 0  | Common Memory Read (16 Bit D15-D0) |

| Х    | 0    | 0    | 1   | 0   | Χ   | 1  | XX    | Х  | Х  | Х  | 0  | Configuration Registers Write      |

| 1    | 0    | 1    | 1   | 0   | Х   | Х  | XX    | Х  | Х  | Х  | Х  | Common Memory Write (8 Bit D7-D0)  |

\_\_\_\_\_

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | А3 | A2 | A1 | Α0 | SELECTED SPACE                       |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|--------------------------------------|

| 0    | 1    | 1    | 1   | 0   | Х   | Х  | XX    | Х  | Χ  | Х  | Χ  | Common Memory Write (8 Bit D15-D8)   |

| 0    | 0    | 1    | 1   | 0   | Х   | Х  | XX    | X  | X  | Х  | 0  | Common Memory Write (16 Bit D15-D0)  |

| Х    | 0    | 0    | 0   | 1   | 0   | 0  | XX    | Χ  | Χ  | Х  | 0  | Card Information Structure Read      |

| 1    | 0    | 0    | 1   | 0   | 0   | 0  | XX    | Х  | Χ  | Х  | 0  | Invalid Access (CIS Write)           |

| 1    | 0    | 0    | 0   | 1   | Х   | Х  | XX    | Х  | Χ  | Х  | 1  | Invalid Access (Odd Attribute Read)  |

| 1    | 0    | 0    | 1   | 0   | Х   | Х  | XX    | Х  | Χ  | Х  | 1  | Invalid Access (Odd Attribute Write) |

| 0    | 1    | 0    | 0   | 1   | Х   | Х  | XX    | Х  | Χ  | Х  | Χ  | Invalid Access (Odd Attribute Read)  |

| 0    | 1    | 0    | 1   | 0   | Х   | Х  | XX    | Х  | Χ  | Х  | Х  | Invalid Access (Odd Attribute Write) |

**Table 3-9. Configuration Registers Decoding**

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | A3 | A2 | A1 | Α0 | SELECTED REGISTER              |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|--------------------------------|

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 0  | 0  | 0  | Configuration Option Reg Read  |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 0  | 0  | 0  | Configuration Option Reg Write |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 0  | 1  | 0  | Card Status Register Read      |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 0  | 1  | 0  | Card Status Register Write     |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 1  | 0  | 0  | Pin Replacement Register Read  |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 1  | 0  | 0  | Pin Replacement Register Write |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 1  | 1  | 0  | Socket and Copy Register Read  |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 1  | 1  | 0  | Socket and Copy Register Write |

**NOTE**: The location of the card configuration registers should always be read from the CIS since these locations may vary in future products. No writes should be performed to the CompactFlash Memory Card attribute memory except to the card configuration register addresses. All other attribute memory locations are reserved.

## **3.4.1.** Attribute Memory Function

Attribute memory is a space where CompactFlash Memory Card CIS and configurations registers are stored, and is limited to 8-bit wide accesses only at even addresses.

As in the Main Memory Read functions, the signals -CE1 and -CE2 control the even-byte and odd-byte address, but only the even-byte data is valid during the Attribute Memory access. Refer to Table 3-10 for signal states and bus validity for the Attribute Memory function.

**Table 3-10. Attribute Memory Function**

| Function Mode                               | -REG | -CE2 | -CE1 | A9 | A0 | -OE | -WE | D15-D8      | D7-D0     |

|---------------------------------------------|------|------|------|----|----|-----|-----|-------------|-----------|

| Standby Mode                                | Χ    | Н    | Н    | X  | X  | Х   | Х   | High Z      | High Z    |

| Read Byte Access CIS ROM (8 bits)           | L    | Н    | L    | L  | L  | L   | Н   | High Z      | Even Byte |

| Write Byte Access CIS (8 bits) (Invalid)    | L    | Н    | L    | L  | L  | Н   | L   | Do not care | Even Byte |

| Read Byte Access<br>Configuration (8 bits)  | L    | Ι    | L    | Н  | L  | L   | Н   | High Z      | Even Byte |

| Write Byte Access<br>Configuration (8 bits) | L    | Н    | L    | Н  | L  | Н   | L   | Do not care | Even Byte |

| Read Word Access CIS (16 bits)              | L    | L    | L    | L  | Х  | L   | Н   | Not Valid   | Even Byte |

| Write Word Access CIS (16 bits) (Invalid)   | L    | L    | L    | L  | X  | Н   | L,  | Do not care | Even Byte |

| Read Word Access<br>Configuration (16 bits) | L    | L    | L    | Н  | Х  | L   | Н   | Not Valid   | Even Byte |

| Function Mode           | -REG | -CE2 | -CE1 | A9 | Α0 | -OE | -WE | D15-D8 | D7-D0     |

|-------------------------|------|------|------|----|----|-----|-----|--------|-----------|

| Write Word Access       | L    | L    | L    | Н  | Х  | Н   | L   | Do not | Even Byte |

| Configuration (16 bits) |      |      |      |    |    |     |     | care   |           |

**NOTE**: The -CE signal or both the -OE signal and the -WE signal must be de-asserted between consecutive cycle operations.

# 3.4.2. Configuration Option Register (Address 200h in Attribute Memory)

The Configuration Option Register is used to configure the cards interface, address decoding and interrupt and to issue a soft reset to the CompactFlash Memory Card.

| Operation | D7     | D6      | D5    | D4    | D3    | D2    | D1    | D0    |

|-----------|--------|---------|-------|-------|-------|-------|-------|-------|

| R/W       | SRESET | LevIREQ | Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 |

#### **SRESET**

Soft Reset—Setting this bit to one (1), waiting the minimum reset width time and returning to zero (0) places the CompactFlash Memory Card in the Reset state. Setting this bit to one (1) is equivalent to assertion of the +RESET signal except that the SRESET bit is not cleared. Returning this bit to zero (0) leaves the CompactFlash Memory Card in the same un-configured, Reset state as following power-up and hardware reset. This bit is set to zero (0) by power-up and hardware reset. Using the PC Card Soft Reset is considered a hard Reset by the ATA Commands. Contrast with Soft Reset in the Device Control Register.

### LevIREQ

This bit is set to one (1) when Level Mode Interrupt is selected, and zero (0) when Pulse Mode is selected. Set to zero (0) by Reset.

**Conf5—Conf0** Configuration Index. Set to zero (0) by reset. It's used to select operation mode of the CompactFlash Memory Card as shown below.

**NOTE**: Conf5 and Conf4 are reserved and must be written as zero (0).

**Table 3-11. Card Configurations**

| Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 | Disk Card Mode                                  |

|-------|-------|-------|-------|-------|-------|-------------------------------------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | Memory Mapped                                   |

| 0     | 0     | 0     | 0     | 0     | 1     | I/O Mapped, Any 16 byte system decoded boundary |

| 0     | 0     | 0     | 0     | 1     | 0     | I/O Mapped, 1F0-1F7/3F6-3F7                     |

| 0     | 0     | 0     | 0     | 1     | 1     | I/O Mapped, 170-177/376-377                     |

# 3.4.3. Card Configuration and Status Register (Address 202h in Attribute Memory)

The Card Configuration and Status Register contain information about the Card's condition.

Table 3-12. Card Configuration and Status Register Organization

| Operation | D7      | D6     | D5    | D4 | D3 | D2     | D1  | D0 |

|-----------|---------|--------|-------|----|----|--------|-----|----|

| Read      | Changed | SigChg | IOis8 | 0  | 0  | PwrDwn | Int | 0  |

| Write     | 0       | SiaCha | IOis8 | 0  | 0  | PwrDwn | 0   | 0  |

### Changed

Indicates that one or both of the Pin Replacement register CRdy, or CWProt bits are set to one (1). When the Changed bit is set, -STSCHG Pin 46 is held low if the SigChg bit is a One (1) and the CompactFlash Memory Card is configured for the I/O interface.

## **SigChg**

This bit is set and reset by the host to enable and disable a state-change "signal" from the Status Register, the Changed bit control pin 46 the Changed Status signal. If no state change signal is desired, this bit should be set to zero (0) and pin 46 (-STSCHG) signal will be held high while the CompactFlash Memory Card is configured for I/O.

#### IOis8

The host sets this bit to a one (1) if the CompactFlash Memory Card is to be configured in an 8-bit I/O mode. The CompactFlash Card is always configured for both 8- and 16-bit I/O, so this bit is ignored.

#### **PwrDwn**

This bit indicates whether the host requests the CompactFlash Memory Card to be in the power saving or active mode. When the bit is one (1), the CompactFlash Card enters a power down mode. When zero (0), the host is requesting the CompactFlash Card to enter the active mode. The PC Card Rdy/-Bsy value becomes BUSY when this bit is changed. Rdy/-Bsy will not become Ready until the power state requested has been entered. The CompactFlash Card automatically powers down when it is idle and powers back up when it receives a command.

#### Int

This bit represents the internal state of the interrupt request. This value is available whether or not I/O interface has been configured. This signal remains true until the condition that caused the interrupt request has been serviced. If interrupts are disabled by the -IEN bit in the Device Control Register, this bit is a zero (0).

## 3.4.4. Pin Replacement Register (Address 204h in Attribute Memory)

Table 3-13. Pin Replacement Register

| Operation | D7 | D6 | D5        | D4     | D3 | D2 | D1        | D0     |

|-----------|----|----|-----------|--------|----|----|-----------|--------|

| Read      | 0  | 0  | CRdy/-Bsy | CWProt | 1  | 1  | RRdy/-Bsy | RWProt |

| Write     | 0  | 0  | CRdy/-Bsy | CWProt | 0  | 0  | MRdy/-Bsy | MWProt |

### CRdv/-Bsv

This bit is set to one (1) when the bit RRdy/-Bsy changes state. This bit can also be written by the host.

### **CWProt**

This bit is set to one (1) when the RWprot changes state. This bit may also be written by the host.

### RRdy/-Bsy

This bit is used to determine the internal state of the Rdy/-Bsy signal. This bit may be used to determine the state of the Ready/-Busy as this pin has been reallocated for use as Interrupt Request on an I/O card. When written, this bit acts as a mask for writing the corresponding bit CRdy/-Bsy.

### **RWProt**