# CGCU/® Technologies

300/300-P Series Industrial Grade SSD

#### **Product Manual**

#### **Cactus Technologies Limited**

Suite C, 15/F, Capital Trade Center 62 Tsun Yip Street, Kwun Tong Kowloon, Hong Kong Tel: +852-2797-2277 Email: sales@cactus-tech.com

#### **Cactus USA**

3112 Windsor Road Suite A356 Austin, Texas 78703 Tel: +512-775-0746 Email: americas@cactus-tech.com

#### Cactus-Tech.com

The information in this manual is believed to be accurate at the time of publication but is subject to change without notice. Cactus Technologies<sup>®</sup> Limited shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or consequential damages resulting from the furnishing, performance, or use of this material.

Cactus Technologies<sup>®</sup> makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Cactus Technologies<sup>®</sup> assume any liability arising out of the application or use of its products, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

Cactus Technologies<sup>®</sup> products are not designed, intended or authorized for use as components in systems intended for surgical implant into the body or in other applications intended to support or sustain life or for any application where the failure of a Cactus Technologies<sup>®</sup> product can result in personal injury or death. Users of Cactus Technologies<sup>®</sup> products for such unintended and unauthorized applications shall assume all risk of such use and shall indemnify and hold Cactus Technologies<sup>®</sup> and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damages, expenses and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended and unauthorized use, even if such claim alleges that Cactus Technologies<sup>®</sup> was negligent regarding the design or manufacture of the part.

All parts of the Cactus Technologies<sup>®</sup> documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior consent, in writing, from Cactus Technologies<sup>®</sup>, Limited.

© 2005-2013 Cactus Technologies Limited. All rights reserved.

# Table of CONTENTS

| 1. Introduction to Cactus Technologies 300/300-P Serie<br>Industrial Grade SSD Products                                  |        |

|--------------------------------------------------------------------------------------------------------------------------|--------|

| 1.1.Supported Standards                                                                                                  |        |

| 1.2.Product Features                                                                                                     |        |

| 1.2.1.Host and Technology Independence                                                                                   |        |

| 1.2.2.Defect and Error Management                                                                                        |        |

| 1.2.3.Intelligent Power Management                                                                                       |        |

| 1.2.4.Power Supply Requirements                                                                                          |        |

| 1.2.4.1 ower Suppry Requirements                                                                                         |        |

| 2 Draduct Chasifications                                                                                                 |        |

| O 2. Product Specifications                                                                                              |        |

| 2.1.System Environmental Specifications                                                                                  |        |

| 2.2.System Power Requirements                                                                                            |        |

| 2.3.System Performance                                                                                                   |        |

| 2.4.System Reliability                                                                                                   |        |

| 2.5.Physical Specifications<br>2.5.1.2.5" SSD Physical Specifications                                                    |        |

| 2.5.2.1.8" SSD Physical Specifications                                                                                   | 0<br>Q |

| 2.6.Capacity Specifications                                                                                              |        |

| 2.0.capacity specifications                                                                                              |        |

| 12 Interface Description                                                                                                 |        |

| O 3. Interface Description                                                                                               |        |

| 3.1.SSD Pin Assignments and Pin Type                                                                                     |        |

| 3.2.Signal Description                                                                                                   |        |

| 3.3.Electrical Specification                                                                                             |        |

| 3.3.1.Absolute Maximum Ratings<br>3.3.2.DC Characteristics                                                               |        |

| 3.3.3.AC Characteristics                                                                                                 |        |

| 3.4.I/O Transfer Function                                                                                                |        |

| 5.4.//O Transfer Function                                                                                                |        |

| A ATA Drive Desister Cat Definition and Drate cal                                                                        |        |

| O 4. ATA Drive Register Set Definition and Protocol                                                                      |        |

| 4.1.Task File Addressing                                                                                                 |        |

| 4.2.ATA Registers                                                                                                        |        |

| 4.2.1.Data Register (Address—1F0[170])                                                                                   |        |

| 4.2.2.Error Register (Address—1F1[171]; Read Only)                                                                       |        |

| 4.2.3.Feature Register (Address—1F1[171]; Write Only)                                                                    |        |

| 4.2.4.Sector Count Register (Address—1F2[172])                                                                           |        |

| 4.2.5.Sector Number (LBA 7-0) Register (Address—1F3[173])                                                                |        |

| 4.2.6.Cylinder Low (LBA 15-8) Register (Address—1F4[174])<br>4.2.7.Cylinder High (LBA 23-16) Register (Address—1F5[175]) |        |

| 4.2.8.Drive/Head (LBA 27-24) Register (Address 1F6[176])                                                                 |        |

| 4.2.9.Status and Alternate Status Registers                                                                              |        |

| (Address 1F7[177] and 3F6[376])                                                                                          | 18     |

| 4.2.10.Device Control Register (Address—3F6[376])                                                                        | 18     |

| 4.2.11.Card (Drive) Address Register (Address 3F7[377])                                                                  |        |

|                                                                                                                          |        |

#### Table of

CONTENTS

| 5. ATA Command Description                                   | 21 |

|--------------------------------------------------------------|----|

| 5.1.ATA Command Set                                          |    |

| 5.1.1.Check Power Mode-98H, E5H                              |    |

| 5.1.2.Execute Drive Diagnostic-90H                           |    |

| 5.1.3.Erase Sector(s)-C0H                                    |    |

| 5.1.4.Format Track-50H                                       |    |

| 5.1.5.Identify Drive-ECH                                     |    |

| 5.1.6.Idle-97H, E3H                                          |    |

| 5.1.7.Idle Immediate-95H, E1H                                |    |

| 5.1.8.Initialize Drive Parameters-91H                        |    |

| 5.1.9.Read Buffer-E4H                                        |    |

| 5.1.10.Read Multiple-C4H<br>5.1.11.Read Long Sector-22H, 23H |    |

| 5.1.12.Read Sector(s)-20H, 21H                               |    |

| 5.1.13.Read Verify Sector(s)-40H, 41H                        |    |

| 5.1.14.Recalibrate-1XH                                       |    |

| 5.1.15.Request Sense-03H                                     |    |

| 5.1.16.Seek-7XH                                              |    |

| 5.1.17.Set Features-EFH                                      |    |

| 5.1.18.Set Multiple Mode-C6H                                 |    |

| 5.1.19.Set Sleep Mode-99H, E6H                               |    |

| 5.1.20.Standby-96H, E2H                                      |    |

| 5.1.21.Standby Immediate-94H, E0H                            |    |

| 5.1.22.Translate Sector-87H                                  |    |

| 5.1.23.Wear Level-F5H                                        |    |

| 5.1.24.Write Buffer-E8H<br>5.1.25.Write Long Sector-23H, 33H |    |

| 5.1.26.Write Multiple Command-CH5                            |    |

| 5.1.27.Write Multiple without Erase-CDH                      |    |

| 5.1.28.Write Sector(s)-30H, 31H.                             |    |

| 5.1.29.Write Sector(s) without Erase-38H                     |    |

| 5.1.30. Write Verify Sector(s)-3CH                           |    |

| 5.2.Error Posting                                            |    |

| Ű                                                            |    |

| 6. 300-P Firmware Specifications                             | 10 |

| 6.1.ATA Mode Security Feature Set                            |    |

| 6.2.CTLock™                                                  |    |

| 6.2.1.Command Structure                                      |    |

| 6.3.CTPurge™                                                 |    |

| 6.3.1.Command Structure                                      |    |

| 6.3.2.Standard Compliance                                    |    |

| 6.3.3.Status Reporting                                       |    |

| 6.3.4.Time and Power Requirements                            |    |

| 6.4.CTWPROT™                                                 |    |

| 6.4.1.Command Structure                                      | 45 |

|                                                              |    |

|                                                              |    |

Appendix A.Ordering Information......46

# Table of CONTENTS Caclus Technologies

| Appendix B.Technical Support Services                                 | 47 |

|-----------------------------------------------------------------------|----|

| • Appendix C.Cactus Technologies <sup>®</sup> Worldwide Sales Offices | 48 |

| • Appendix D.Limited Warranty                                         | 49 |

Introduction to Cactus Technologies 300/300-P Series Industrial Grade SSD Products

#### **Features**

- Solid state design with no moving parts

- Industry standard 2.5" or 1.8" IDE Drive form factor

- Supports ATA PIO Modes 0-4

- Supports MultiWord DMA Modes 0-2

- Supports UDMA Modes 0-4

- High reliability, MTBF > 4,000,000 hrs.

- Enhanced error correction, < 1 error in 10<sup>14</sup> bits read

- Intelligent power management to reduce power consumption

- Dual voltage support: 3.3V/5.0V

#### **Overview**

The Cactus Technologies Solid State Drive(SSD) is a high capacity solid-state flash memory product that complies with the ANSI ATA standard and is electrically compatible with an IDE disk drive. Cactus SSDs provide up to 32GB of formatted storage capacity in both 2.5" and 1.8" form factors.

The Cactus Technologies Industrial Grade SSD products use high quality flash memory from well known vendors, such as Samsung Corporation. In addition, it include an on-drive intelligent controller that manages interface protocols, data storage and retrieval as well as ECC, defect handling and diagnostics, power management, and clock control. The controller's firmware is upgradeable, thus allowing feature enhancements and firmware updates in the field.

# Additional features for 300-P series

- ATA Security Feature Set

- CTLock<sup>™</sup>. This feature allows the card to be locked to a specific host.

- CTPurge<sup>™</sup>. This feature allows the host to securely erase the contents of the card using procedures in published standards.

- CTWProt<sup>™</sup>. This feature allows for both software and hardware initiated write protect function.

# 1.1. Supported Standards

Cactus Technologies SSD is fully electrically compatible with the following specification:

• ATA 5 Specification published by ANSI: X3.221 AT Attachment Interface for Disk Drives

#### 1.2. Product Features

Cactus Technologies Industrial SSD contains a high level, intelligent controller. This intelligent controller provides many capabilities including the following:

- Standard ATA register and command set (same as found on most magnetic disk drives).

- Manages details of erasing and programming flash memory independent of the host system

- · Sophisticated defect managing capabilities (similar to magnetic disk drives).

- Sophisticated system for error recovery using powerful error correction code (ECC).

- Intelligent power management for low power operation.

#### 1.2.1. Host and Technology Independence

Cactus Technologies Industrial SSD appears as a standard ATA disk drive to the host system. The drive utilizes a 512-byte sector which is the same as that in an IDE magnetic disk drive. To write or read a sector (or multiple sectors), the host computer software simply issues an ATA Read or Write command to the drive as per the ATA protocol. The host software then waits for the command to complete. The host system does not get involved in the details of how the flash memory is erased, programmed or read as this is all managed by the built-in controller in the drive. Also, with the intelligent on-board controller, the host system software will not require changing as new flash memory evolves. Thus, systems that support the Cactus Technologies Industrial SSD products today will continue to work with future Cactus Technologies Industrial SSDs built with new flash technology without having to update or change host software.

# 1.2.2. Defect and Error Management

Cactus Technologies Industrial SSD contains a sophisticated defect and error management system similar to those found in magnetic disk drives. The defect management is completely transparent to the host and does not consume any user data space.

The soft error rate for Cactus Technologies Industrial SSDs is much lower than that of magnetic disk drives. In the extremely rare case where a read error does occur, the drive has sophisticated ECC to recover the data.

These defect and error management systems, coupled with the solid-state construction, give Cactus Technologies Industrial SSDs unparalleled reliability.

# 1.2.3. Intelligent Power Management

Cactus Technologies SSDs employ sophisticated power management algorithms to conserve power. Upon completion of a command, the drive will automatically enter sleep mode if no further commands are received. In most situations, the drive will be in sleep mode except when the host is accessing it, thus conserving power.

When the drive is in sleep mode, any command issued to the drive will cause it to exit sleep and respond.

#### 1.2.4. Power Supply Requirements

Cactus Technologies Industrial SSD is a dual voltage product, which means it will operate at a voltage range of 3.30 volts  $\pm 10\%$  or 5.00 volts  $\pm 10\%$ .

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

#### System Environmental Specifications

| Table 2-1. Environmental Sp         | Cactus Industrial SSD      |                                                          |

|-------------------------------------|----------------------------|----------------------------------------------------------|

| Temperature                         | Operating:                 | 0° C to +70° C (Standard)<br>-45° C to +90° C (Extended) |

| -> Humidity                         | Operating & Non-Operating: | 8% to 95%, non-condensing                                |

| left Acoustic Noise                 |                            | 0 dB                                                     |

| ➡ Vibration                         | Operating & Non-Operating: | 20 G MIL-STD-883G Method 2005.2 condition A              |

| Shock                               | Operating & Non-Operating: | 3,000 G MIL-STD-883G Method 2002.3 condition C           |

| Altitude<br>(relative to sea level) | Operating & Non-Operating: | 100,000 feet maximum                                     |

#### System Power Requirements

| Table 2-2. Power Requirements                      |          | Cactus Industrial SSD |

|----------------------------------------------------|----------|-----------------------|

| DC Input Voltage (VCC)<br>100 mV max. ripple (p-p) |          | 5.0V ±10%             |

|                                                    | Sleep:   | 800 μΑ                |

| (Maximum Average Value)                            | Reading: | 220 mA                |

| See Notes.                                         | Writing: | 180 mA                |

NOTES: All values quoted are typical at ambient temperature and nominal supply voltage unless otherwise stated.

Sleep mode is specified under the condition that all drive inputs are static CMOS levels and in a "Not Busy" operating state.

4

#### 2.3. System Performance

All performance numbers are typical values assuming the card controller is in the default (i.e., fastest) mode.

#### Table 2-3. Performance

| 😔 Start Up Times      | Reset to ready: | 35 msec typical         |

|-----------------------|-----------------|-------------------------|

| 😔 Read Transfer Rate  |                 | up to 35.0 Mbytes/sec*  |

| 😔 Write Transfer Rate |                 | up to 20.0 Mbytes/sec * |

| 😔 Controller Overhead | Command to DRQ  | 2 msec maximum          |

# 2.4. System Reliability

Table 2-4. Reliability

| → MTBF (@ 25°C)    | >4,000,000 hours                                       |

|--------------------|--------------------------------------------------------|

| 😔 Data Reliability | <1 non-recoverable error in 10 <sup>14</sup> bits READ |

| 😔 Endurance:       | >2,000,000 erase/program cycles                        |

# 2.5. Physical Specifications

The following sections provide the physical specifications for Cactus Technologies Industrial SSD products.

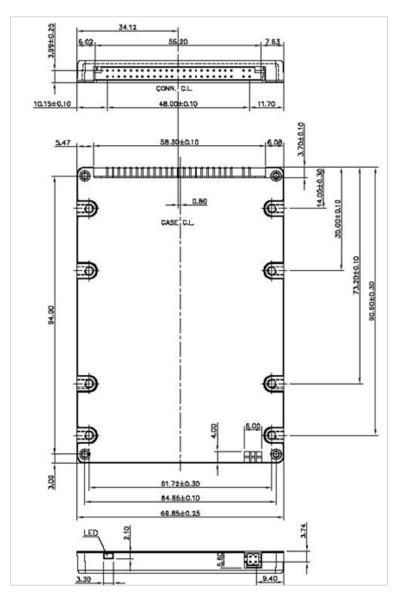

# 2.5.1. 2.5" SSD Physical Specifications

Figure 2-1. 2.5" SSD Dimensions

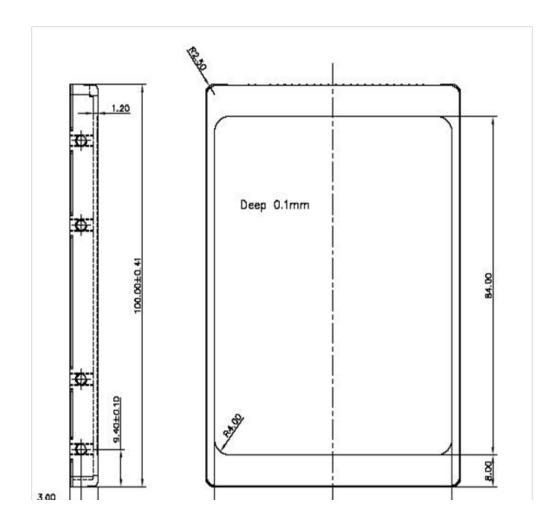

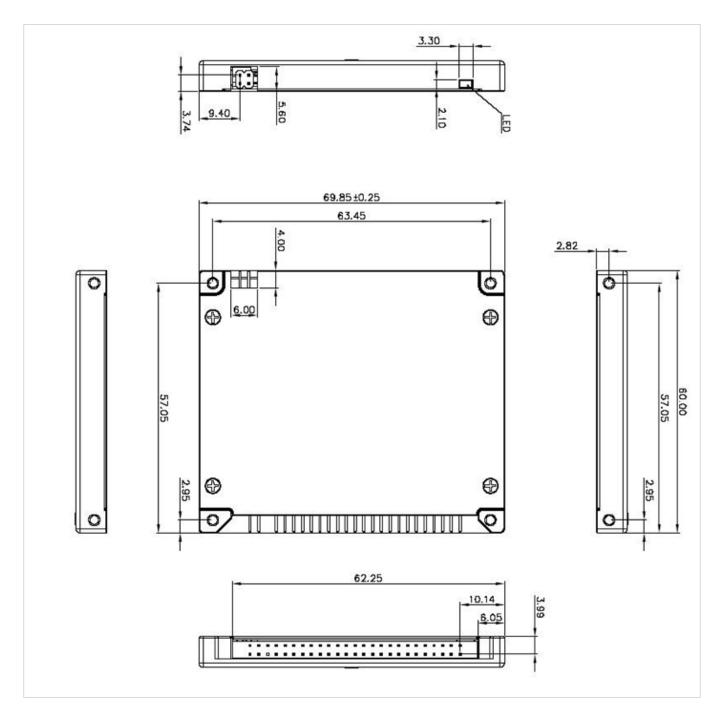

#### • 2.5.2. 1.8" SSD Physical Specifications

#### Figure 2-2. 1.8" SSD Dimensions

# 2.6. Capacity Specifications

Table 2-5 shows the specific capacity for the various models and the default number of heads, sectors/track and cylinders.

#### Table 2-5. Model Capacities

| Capacity | Capacity (formatted) | Sectors/<br>Drive (Max<br>LBA+1) | No. of<br>Heads | No. of<br>Sectors/<br>Track | No. of<br>Cylinders |

|----------|----------------------|----------------------------------|-----------------|-----------------------------|---------------------|

| 128MB    | 129,761,280 bytes    | 253,440                          | 8               | 32                          | 990                 |

| 256MB    | 259,522,560 bytes    | 506,880                          | 16              | 32                          | 990                 |

| 512MB    | 521,256,960 bytes    | 1018080                          | 16              | 63                          | 1,010               |

| 1GB      | 1,047,674,880 bytes  | 2,046,240                        | 16              | 63                          | 2,030               |

| 2GB      | 2,097,930,240 bytes  | 4,097,520                        | 16              | 63                          | 4,065               |

| 4GB      | 4,224,245,760 bytes  | 8,250,480                        | 16              | 63                          | 8,185               |

| 8GB      | 8,456,749,056 bytes  | 16,517,088                       | 16              | 63                          | 16,386              |

| 16GB     | 16,829,890,560 bytes | 32,870,880                       | 16              | 63                          | 32,610              |

| 32GB     | 32,978,534,400 bytes | 64,411,200                       | 16              | 63                          | 63,900              |

The following sections provide detailed information on the Cactus Technologies Industrial SSD interface.

#### 3.1. SSD Pin Assignments and Pin Type

The signal/pin assignments are listed in Table 3-6. Low active signals have a "-" prefix. Pin types are Input, Output or Input/Output. Sections 3.3.1 to 3.3.4 define the DC characteristics for all input and output type structures.

| Pin | Signal                         | Pin  | Pin | Signal     | Pin  |

|-----|--------------------------------|------|-----|------------|------|

| Num | Name                           | Туре | Num | Name       | Туре |

| 1   | -Reset                         | I    | 2   | GND        |      |

| 3   | Data 7                         | I/O  | 4   | Data 8     | I/O  |

| 5   | Data 6                         | I/O  | 6   | Data 9     | I/O  |

| 7   | Data 5                         | I/O  | 8   | Data 10    | I/O  |

| 9   | Data 4                         | I/O  | 10  | Data 11    | I/O  |

| 11  | Data 3                         | I/O  | 12  | Data 12    | I/O  |

| 13  | Data 2                         | I/O  | 14  | Data 13    | I/O  |

| 15  | Data 1                         | I/O  | 16  | Data 14    | I/O  |

| 17  | Data 0                         | I/O  | 18  | Data 15    | I/O  |

| 19  | GND                            |      | 20  | Key        |      |

| 21  | -DMARQ                         | 0    | 22  | GND        |      |

| 23  | -IOW/STOP                      |      | 24  | GND        |      |

| 25  | -IOR/<br>-HDMARDY/<br>HSTROBE  | I    | 26  | GND        |      |

| 27  | IORDY/<br>-DDMARDY/<br>DSTROBE | 0    | 28  | -CSEL      | I    |

| 29  | -DMACK                         |      | 30  | GND        |      |

| 31  | IRQ                            | 0    | 32  | (reserved) |      |

| 33  | A1                             |      | 34  | -PDIAG     | I/O  |

| 35  | A0                             | I    | 36  | A2         | I    |

| 37  | -CS0                           |      | 38  | -CS1       | I    |

| 39  | -DASP                          | I/O  | 40  | GND        |      |

| 41  | Vcc                            |      | 42  | Vcc        |      |

| 43  | GND                            |      | 44  | Reserved   |      |

Table 3-6. SSD Pin Assignments and Pin Type

# 3.2. Signal Description

Table 3-7 describes the I/O signals. Signals whose source is the host are designated as inputs while signals that the SSD sources are outputs. The SSD logic levels conform to those specified in the ANSI ATA Specification.

| Table 3-7. | Signal | Description |

|------------|--------|-------------|

|------------|--------|-------------|

| Signal Name                | Dir. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2—A0                      | I    | A[2:0] is used to select the one of eight registers in the Task File.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -PDIAG                     | I/O  | This input/output is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -DASP                      | I/O  | This input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -CS0, -CS1                 | I    | -CS0 is the chip select for the task file registers while -CS1 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                                                                                                                                                                                                                                                                      |

| -CSEL                      | I    | This internally pulled up signal is used to configure this device<br>as a Master or a Slave. When this pin is grounded, this device<br>is configured as a Master. When the pin is open, this device is<br>configured as a Slave.                                                                                                                                                                                                                                                                                                     |

| D15—D00                    | I/O  | These lines carry the Data, Commands and Status information<br>between the host and the controller. D00 is the LSB of the Even Byte<br>of the Word. D08 is the LSB of the Odd Byte of the Word. All Task<br>File operations occur in byte mode on the low order bus D00-D07<br>while all data transfers are 16 bits using D00-D15.                                                                                                                                                                                                   |

| GND                        |      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| -IORD/-HDMARDY/<br>HSTROBE | I    | This is an I/O Read strobe generated by the host for PIO data-in and<br>register transfers. Data is latched by the host on the rising edge of<br>this signal.<br>-HDMARDY is a flow control signal for UDMA data-in transfers.<br>This signal is asserted by the host to indicate to the device that it is<br>ready to accept data. The host may negate this signal to pause the<br>trasnfer.<br>HSTROBE is a strobe signal generated by the host for UDMA data-<br>out transfers. Data is transferred on both edges of this signal. |

| Signal Name                 | Dir. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IOWR/STOP                  | I    | The I/O Write strobe pulse is used to clock I/O data on the Data bus<br>into the SSD for PIO data-out and register transfers. Data is latched<br>by the device on the rising edge of this signal.<br>In UDMA transfers, STOP is asserted by the host to signal the<br>termination of the UDMA burst.                                                                                                                                                                                  |

| INTRQ                       | 0    | This signal is the active high Interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -RESET                      | I    | This input pin is the active low hardware reset from the host.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| vcc                         |      | +5 V, +3.3 V power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -IORDY/-DDMARDY/<br>DSTROBE | 0    | The -IORDY signal is driven by the SSD to extend the I/O cycle in<br>progress for PIO modes 3 and above.<br>-DDMARDY is a flow control signal for UDMA data-out transfers.<br>This signal is asserted by the device to signal to the host that it is<br>ready to accept data. The device may negate this signal to pause<br>the transfer.<br>DSTROBE is a data strobe signal generated by the device for UDMA<br>data-in transfers. Data is transferred on both edges of this signal. |

| DMARQ                       | 0    | This signal is generated by the device to request MWDMA or UDMA transfers.                                                                                                                                                                                                                                                                                                                                                                                                            |

| -DMACK                      | I    | This signal is asserted by the host to acknowledge a DMARQ from the device.                                                                                                                                                                                                                                                                                                                                                                                                           |

# 3.3. Electrical Specification

The following table defines all D.C. Characteristics for the SSD Series. Unless otherwise stated, conditions are:

Vcc = 5V ± 10% or Vcc = 3.3V ± 10% Ta = -45°C to 90°C

#### • 3.3.1. Absolute Maximum Ratings

| Parameter               | Symbol | MIN  | MAX  | Units |

|-------------------------|--------|------|------|-------|

| Storage Temperature     | Ts     | -65  | +150 | °C    |

| Operating Temperature   | TA     | -45  | +90  | °C    |

| Vcc with respect to GND | Vcc    | -0.3 | 6.5  | V     |

#### • 3.3.2. DC Characteristics

| Parameter                       | Symbol                         | MIN  | MAX        | Units |

|---------------------------------|--------------------------------|------|------------|-------|

| Input Voltage                   | Vin                            | -0.5 | Vcc + 0.5  | V     |

| Output Voltage                  | Vout                           | -0.3 | Vcc + 0.3  | V     |

| Input Leakage Current           | lu                             | -10  | 10         | uA    |

| Output Leakage Current          | ILO                            | -10  | 10         | uA    |

| Input/Output Capacitance        | C <sub>I</sub> /C <sub>o</sub> |      | 10         | pF    |

| Operating Current<br>Sleep Mode | I <sub>cc</sub>                |      |            | mA    |

| Active                          |                                |      | 0,8<br>220 |       |

#### ➡ 3.3.3. AC Characteristics

Cactus SSD products conforms to all AC timing requirements as specified in the ANSI ATA specifications. Please refer to that document for details of AC timing for all operation modes of the device.

# 3.4. I/O Transfer Function

Table 3-7 SSD I/O Function

| Function Code             | -CE2 | -CE1 | Address | -IORD | -IOWR | D15-D8          | D7-D0            |  |

|---------------------------|------|------|---------|-------|-------|-----------------|------------------|--|

| Invalid Mode              | L    | L    | Х       | Х     | Х     | High Z          | High Z           |  |

| Standby Mode              | н    | Н    | Х       | Х     | Х     | High Z          | High Z           |  |

| Task File Write           | Н    | L    | 1-7h    | Н     | L     | Do not care     | Data In          |  |

| Task File Read            | Н    | L    | 1-7h    | L     | Н     | High Z          | Data Out         |  |

| Data Register<br>Write    | н    | L    | 0       | Н     | L     | Odd-Byte<br>In  | Even-Byte<br>In  |  |

| Data Register<br>Read     | н    | L    | 0       | L     | Н     | Odd-Byte<br>Out | Even-Byte<br>Out |  |

| Control Register<br>Write | L    | Н    | 6h      | Н     | L     | Do not care     | Control In       |  |

| Alt Status Read           | L    | Н    | 6h      | L     | Н     | High Z          | Status Out       |  |

The communication to or from the SSD is done using the Task File registers, which provide all the necessary registers for control and status information. The ATA interface connects peripherals to the host using four register mapping methods. Table 4-8 is a detailed description of these methods.

#### Table 4-8. I/O Configurations

| Address          | Drive # | Description                  |

|------------------|---------|------------------------------|

| 1F0-1F7, 3F6-3F7 | 0       | Primary I/O Mapped Drive 0   |

| 1F0-1F7, 3F6-3F7 | 1       | Primary I/O Mapped Drive 1   |

| 170-177, 376-377 | 0       | Secondary I/O Mapped Drive 0 |

| 170-177, 376-377 | 1       | Secondary I/O Mapped Drive 1 |

#### 4.1. Task File Addressing

I/O decoding to access the task file registers is as listed in Table 4-9.

| -CE2 | -CE1 | A2 | A1 | <b>A</b> 0 | -IORD=0                | -IOWR=0                |

|------|------|----|----|------------|------------------------|------------------------|

| 1    | 0    | 0  | 0  | 0          | RD Data                | WR Data                |

| 1    | 0    | 0  | 0  | 1          | Error Register         | Features               |

| 1    | 0    | 0  | 1  | 0          | Sector Count           | Sector Count           |

| 1    | 0    | 0  | 1  | 1          | Sector No./LBA low     | Sector No./LBA low     |

| 1    | 0    | 1  | 0  | 0          | Cylinder Low/LBA mid   | Cylinder Low/ LBA mid  |

| 1    | 0    | 1  | 0  | 1          | Cylinder High/LBA high | Cylinder High/LBA high |

| 1    | 0    | 1  | 1  | 0          | Select Drive/Head      | Select Drive/Head      |

| 1    | 0    | 1  | 1  | 1          | Status                 | Command                |

| 0    | 1    | 1  | 1  | 0          | Alt Status             | Device Control         |

| 0    | 1    | 1  | 1  | 1          | Drive Address          | Reserved               |

#### Table 4-9. Task File I/O Decoding

#### 4.2. ATA Registers

#### • 4.2.1. Data Register (Address-1F0[170])

The Data Register is a 16-bit register, and it is used to transfer data blocks between the SSD data buffer and the Host.

#### • 4.2.2. Error Register (Address-1F1[171]; Read Only)

This register contains additional information about the source of an error when an error is indicated in bit 0 of the Status register. The bits are defined as follows:

| D7         | D6                                                                             | D5                                                      | D4                          | D3            | D2   | D1 | D0                          |  |  |  |  |

|------------|--------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------|---------------|------|----|-----------------------------|--|--|--|--|

| BBK        | UNC                                                                            | 0                                                       | IDNF                        | 0             | ABRT | 0  | AMNF                        |  |  |  |  |

| Bit 7 (BBk | () This b                                                                      | it is set whe                                           | n a Bad Bloc                | k is detected | d.   |    |                             |  |  |  |  |

| Bit 6 (UN  | <b>Bit 6 (UNC)</b> This bit is set when an Uncorrectable Error is encountered. |                                                         |                             |               |      |    |                             |  |  |  |  |

| Bit 5      | This b                                                                         | This bit is 0.                                          |                             |               |      |    |                             |  |  |  |  |

| Bit 4 (IDN | I <b>F)</b> The re                                                             | The requested sector ID is in error or cannot be found. |                             |               |      |    |                             |  |  |  |  |

| Bit 3      | This b                                                                         | it is 0.                                                |                             |               |      |    |                             |  |  |  |  |

| Bit 2 (Abo |                                                                                |                                                         | e command<br>Fault, etc.) o |               |      |    | us condition:<br>en issued. |  |  |  |  |

| Bit 1      | This b                                                                         | This bit is 0.                                          |                             |               |      |    |                             |  |  |  |  |

| Bit 0 (AM  | <b>NF)</b> This b                                                              | it is set in ca                                         | ase of a gene               | eral error.   |      |    |                             |  |  |  |  |

#### • 4.2.3. Feature Register (Address-1F1[171]; Write Only)

This register provides information regarding features of the SSD that the host can utilize.

#### • 4.2.4. Sector Count Register (Address-1F2[172])

This register contains the number of sectors of data requested to be transferred on a read or write operation between the host and the SSD. If the value in this register is zero, a count of 256 sectors is specified. If the command was successful, this register is zero at command completion. If not successfully completed, the register contains the number of sectors that need to be transferred in order to complete the request.

#### • 4.2.5. Sector Number (LBA 7-0) Register (Address-1F3[173])

This register contains the starting sector number or bits 7-0 of the Logical Block Address (LBA) for any SSD data access for the subsequent command.

#### • 4.2.6. Cylinder Low (LBA 15-8) Register (Address-1F4[174])

This register contains the low order 8 bits of the starting cylinder address or bits 15-8 of the Logical Block Address.

# • 4.2.7. Cylinder High (LBA 23-16) Register (Address-1F5[175])

This register contains the high order bits of the starting cylinder address or bits 23-16 of the Logical Block Address.

#### • 4.2.8. Drive/Head (LBA 27-24) Register (Address 1F6[176])

The Drive/Head register is used to select the drive and head. It is also used to select LBA addressing instead of cylinder/head/sector addressing. The bits are defined as follows:

| D7 | D6  | D5 | D4  | D3  | D2  | D1  | D0  |

|----|-----|----|-----|-----|-----|-----|-----|

| 1  | LBA | 1  | DRV | HS3 | HS2 | HS1 | HS0 |

Bit 7 This bit is set to 1.

**Bit 6** LBA is a flag to select either Cylinder/Head/Sector (CHS) or Logical Block Address Mode (LBA). When LBA=0, Cylinder/Head/Sector mode is selected. When LBA=1, Logical Block Address is selected. In Logical Block Mode, the Logical Block Address is interpreted as follows:

LBA07-LBA00: Sector Number Register D7-D0.

LBA15-LBA08: Cylinder Low Register D7-D0.

LBA23-LBA16: Cylinder High Register D7-D0.

LBA27-LBA24: Drive/Head Register bits HS3-HS0.

- Bit 5 This bit is set to 1.

- **Bit 4 (DRV)** This bit will have the following meaning. DRV is the drive number. When DRV=0, drive 0 is selected When DRV=1, drive 1 is selected.

- **Bit 3 (HS3)** When operating in the Cylinder, Head, Sector mode, this is bit 3 of the head number. It is Bit 27 in the Logical Block Address mode.

- **Bit 2 (HS2)** When operating in the Cylinder, Head, Sector mode, this is bit 2 of the head number. It is Bit 26 in the Logical Block Address mode.

- **Bit 1 (HS1)** When operating in the Cylinder, Head, Sector mode, this is bit 1 of the head number. It is Bit 25 in the Logical Block Address mode.

- **Bit 0 (HS0)** When operating in the Cylinder, Head, Sector mode, this is bit 0 of the head number. It is Bit 24 in the Logical Block Address mode.

# • 4.2.9. Status and Alternate Status Registers (Address 1F7[177] and 3F6[376])

These registers return the status when read by the host. Reading the Status register does clear a pending interrupt while reading the Auxiliary Status register does not. The meaning of the status bits are described as follows:

| D7                       | D6                | D5                                                                                                                                                              | D4        | D3                           | D2   | D1 | D0                            |  |  |

|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------|------|----|-------------------------------|--|--|

| BUSY                     | RDY               | DWF                                                                                                                                                             | DSC       | DRQ                          | CORR | 0  | ERR                           |  |  |

| Bit 7 (BUS<br>Bit 6 (RD) |                   |                                                                                                                                                                 |           |                              |      |    |                               |  |  |

|                          |                   | requested by the host. This bit is cleared at power up and remains cleared un<br>the device is ready to accept a command.                                       |           |                              |      |    |                               |  |  |

| Bit 5 (DW                | <b>(F)</b> This b | This bit, if set, indicates a write fault has occurred.                                                                                                         |           |                              |      |    |                               |  |  |

| Bit 4 (DSC               | C) This b         | This bit is set when the device is ready.                                                                                                                       |           |                              |      |    |                               |  |  |

| Bit 3 (DRO               |                   |                                                                                                                                                                 |           | the device r<br>he host thro |      |    | ı be                          |  |  |

| Bit 2 (COI               | has be            | This bit is set when a Correctable data error has been encountered and the has been corrected. This condition does not terminate a multi-sector read operation. |           |                              |      |    |                               |  |  |

| Bit 1 (IDX               | X) This b         | it is always s                                                                                                                                                  | set to 0. |                              |      |    |                               |  |  |

| Bit 0 (ERR               |                   |                                                                                                                                                                 |           | us commane<br>in additiona   |      |    | be of error. Th<br>the error. |  |  |

#### 4.2.10. Device Control Register (Address-3F6[376])

This register is used to control the drive interrupt request and to issue an ATA soft reset to the drive. The bits are defined as follows:

| D7  | D6 | D5 | D4 | D3 | D2     | D1   | D0 |

|-----|----|----|----|----|--------|------|----|

| HOB | Х  | Х  | Х  | 1  | SW Rst | -IEn | 0  |

- **Bit 7** This bit is used in 48-bit addressing mode. When cleared, the host can read the most recently written values of the Sector Count,Drive/Head and LBA registers. When set, the host will read the previous written values of these registers. A write to any Command block register will clear this bit.

- Bit 6 This bit is an X (Do not care).

- Bit 5 This bit is an X (Do not care).

- Bit 4 This bit is an X (Do not care).

- **Bit 3** This bit is ignored by the drive.

- **Bit 2 (SW Rst)** This bit is set to 1 in order to force the drive to perform an AT Disk controller Soft Reset operation. The drive remains in Reset until this bit is reset to '0'.

- **Bit 1 (-IEn)** The Interrupt Enable bit enables interrupts when the bit is 0. When the bit is 1, interrupts from the drive are disabled. This bit is set to 0 at power on and Reset.

- **Bit 0** This bit is ignored by the drive.

#### • 4.2.11. Drive Address Register (Address 3F7[377])

This register is provided for compatibility with the AT disk drive interface. It is recommended that this register not be mapped into the host's I/O space because of potential conflicts on Bit 7. The bits are defined as follows:

| D7 | D6   | D5   | D4   | D3   | D2   | D1    | D0    |

|----|------|------|------|------|------|-------|-------|

| Х  | -WTG | -HS3 | -HS2 | -HS1 | -HSO | -nDS1 | -nDS0 |

Bit 7 This bit is unknown.

Implementation Note:

Conflicts may occur on the host data bus when this bit is provided by a Floppy Disk Controller operating at the same addresses as the SSD. Following are some possible solutions to this problem:

1. Locate the SSD at a non-conflicting address (i.e., Secondary address (377) when a Floppy Disk Controller is located at the Primary addresses).

2. Do not install a Floppy and a SSD in the system at the same time.

3. Implement a socket adapter that can be programmed to (conditionally) tri-state D7 of I/O address 3F7/377 when a SSD product is installed and conversely to tri-state D6-D0 of I/O address 3F7/377 when a floppy controller is installed.

4. Do not use the SSD's Drive Address register. This may be accomplished by either a) If possible, program the host adapter to enable only I/O addresses 1F0-1F7, 3F6 (or 170-177, 176) to the SSD or b) if provided use an additional Primary/Secondary configuration in the SSD that does not respond to accesses to I/O locations 3F7 and 377. With either of these implementations, the host software must not attempt to use information in the Drive Address Register.

- **Bit 6 (-WTG)** This bit is 0 when a write operation is in progress, otherwise, it is 1.

- **Bit 5 (-HS3)** This bit is the negation of bit 3 in the Drive/Head register.

- **Bit 4 (-HS2)** This bit is the negation of bit 2 in the Drive/Head register.

- **Bit 3 (-HS1)** This bit is the negation of bit 1 in the Drive/Head register.

- **Bit 2 (-HS0)** This bit is the negation of bit 0 in the Drive/Head register.

- **Bit 1 (-nDS1)** This bit is 0 when drive 1 is active and selected.

- **Bit 0 (-nDS0)** This bit is 0 when the drive 0 is active and selected.

This section defines the software requirements and the format of the commands the host sends to the Industrial SSD products. Commands are issued by loading the required registers in the command block with the supplied parameters, and then writing the command code to the Command Register. The manner in which a command is accepted varies. There are three classes (see Table 5-10) of command acceptance, all dependent on the host not issuing commands unless the drive is not busy. (The BUSY bit in the status and alternate status registers is 0.)

- Upon receipt of a Class 1 command, the drive sets the BUSY bit within 400 nsec.

- Upon receipt of a Class 2 command, the drive sets the BUSY bit within 400 nsec, sets up the sector buffer for a write operation, sets DRQ within 700 µsec, and clears the BUSY bit within 400 nsec of setting DRQ.

- Upon receipt of a Class 3 command, the drive sets the BUSY bit within 400 nsec, sets up the sector buffer for a write operation, sets DRQ within 20 msec (assuming no re-assignments), and clears the BUSY bit within 400 nsec of setting DRQ.

#### 5.1. ATA Command Set

Table 5-10 summarizes the supported ATA command set with the paragraphs that follow describing the individual commands and the task file for each.

| Class | COMMAND                     | Code       | FR | SC | SN | CY | DH | LBA |

|-------|-----------------------------|------------|----|----|----|----|----|-----|

| 1     | Check Power Mode            | E5h or 98h | -  | -  | -  | -  | D  | -   |

| 1     | Execute Drive Diagnostic    | 90h        | -  | -  | -  | -  | -  | -   |

| 1     | Erase Sector(s)             | C0h        | -  | Y  | Y  | Y  | Y  | Y   |

| 2     | Format Track                | 50h        | -  | Y  | -  | Y  | Y  | Y   |

| 1     | Identify Drive              | ECh        | -  | -  | -  | -  | D  | -   |

| 1     | Idle                        | E3h or 97h | -  | Y  | -  | -  | D  | -   |

| 1     | Idle Immediate              | E1h or 95h | -  | -  | -  | -  | D  | -   |

| 1     | Initialize Drive Parameters | 91h        | -  | Y  | -  | -  | Y  | -   |

| 1     | Read Buffer                 | E4h        | -  | -  | -  | -  | D  | -   |

| 1     | Read Multiple               | C4h        | -  | Y  | Y  | Υ  | Y  | Y   |

| 1     | Read Long Sector            | 22h or 23h | -  | -  | Y  | Y  | Y  | Y   |

| 1     | Read Sector(s)              | 20h or 21h | -  | Y  | Y  | Y  | Y  | Y   |

| 1     | Read Verify Sector(s)       | 40h or 41h | -  | Y  | Y  | Y  | Y  | Y   |

| 1     | Recalibrate                 | 1Xh        | -  | -  | -  | -  | D  | -   |

| 1     | Request Sense               | 03h        | -  | -  | -  | -  | D  | -   |

| 1     | Seek                        | 7Xh        | -  | -  | Y  | Y  | Y  | Y   |

| 1     | Set Features                | EFh        | Y  | -  | -  | -  | D  | -   |

| 1     | Set Multiple Mode           | C6h        | -  | Y  | -  | -  | D  | -   |

#### Table 5-10. ATA Command Set

| Class | COMMAND                   | Code       | FR | SC | SN | CY | DH | LBA |

|-------|---------------------------|------------|----|----|----|----|----|-----|

| 1     | Set Sleep Mode            | E6h or 99h | -  | -  | -  | -  | D  | -   |

| 1     | Stand By                  | E2h or 96h | -  | -  | -  | -  | D  | -   |

| 1     | Stand By Immediate        | E0h or 94h | -  | -  | -  | -  | D  | -   |

| 1     | Translate Sector          | 87h        | -  | Y  | Y  | Y  | Y  | Y   |

| 1     | Wear Level                | F5h        | -  | -  | -  | -  | Y  | -   |

| 2     | Write Buffer              | E8h        | -  | -  | -  | -  | D  | -   |

| 2     | Write Long Sector         | 32h or 33h | -  | -  | Y  | Y  | Y  | Y   |

| 3     | Write Multiple            | C5h        | -  | Y  | Y  | Y  | Y  | Y   |

| 3     | Write Multiple w/o Erase  | CDh        | -  | Y  | Y  | Y  | Y  | Y   |

| 2     | Write Sector(s)           | 30h or 31h | -  | Y  | Y  | Y  | Y  | Y   |

| 2     | Write Sector(s) w/o Erase | 38h        | -  | Y  | Y  | Y  | Y  | Y   |

| 2     | Write Verify Sector(s)    | 3Ch        | -  | Y  | Y  | Υ  | Y  | Y   |

#### Definitions: FR = Features Register, SC = Sector Count Register, SN = Sector Number Register, CY = Cylinder Registers, DH = Drive/Drive/Head Register, LBA = Logical Block Address Mode Supported (see command descriptions for use).

Y—The register contains a valid parameter for this command. For the Drive/Head Register Y means both the drive and head parameters are used; D—only the drive parameter is valid and not the head parameter.

#### 5.1.1. Check Power Mode-98H, E5H

The Check Power Mode command in Table 5-11 checks the power mode.

| Bit ->       | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

|--------------|---|---|---|-------|-------|---|---|---|

| Command (7)  |   |   |   | E5H o | r 98H |   |   |   |

| C/D/H (6)    |   | Х |   | Drive |       | > | X |   |

| Cyl High (5) |   |   |   | >     | <     |   |   |   |

| Cyl Low (4)  |   |   |   | >     | <     |   |   |   |

| Sec Num (3)  |   |   |   | >     | <     |   |   |   |

| Sec Cnt (2)  |   |   |   | >     | <     |   |   |   |

| Feature (1)  |   |   |   | >     | <     |   |   |   |

#### Table 5-11. Check Power Mode

If the drive is in, going to, or recovering from the standby mode, the drive sets BSY, sets the Sector Count Register to 00h, clears BSY and generates an interrupt. If the drive is in active mode, the drive sets BSY, sets the Sector Count Register to FFh, clears BSY and generates an interrupt.

#### 5.1.2. Execute Drive Diagnostic-90H

The Executive Drive Diagnostic command in Table 5-12 performs the internal diagnostic tests implemented by the drive.

| Bit ->       | 7 | 6 | 5 | 4     | 3  | 2 | 1 | 0 |

|--------------|---|---|---|-------|----|---|---|---|

| Command (7)  |   |   |   | 90    | )H |   |   |   |

| C/D/H (6)    |   | Х |   | Drive |    | > | < |   |

| Cyl High (5) |   |   |   | >     | <  |   |   |   |

| Cyl Low (4)  |   |   |   | >     | K  |   |   |   |

| Sec Num (3)  |   |   |   | >     | <  |   |   |   |

| Sec Cnt (2)  |   |   |   | >     | K  |   |   |   |

| Feature (1)  |   |   |   | >     | K  |   |   |   |

Table 5-12. Executive Drive Diagnostic

A code of 01h will be returned in the Error Register at the end of the command.

#### ➡ 5.1.3. Erase Sector(s)-C0H

Table 5-13. Erase Sectors

| Bit ->       | 7 | 6            | 5 | 4            | 3           | 2        | 1         | 0 |  |  |

|--------------|---|--------------|---|--------------|-------------|----------|-----------|---|--|--|

| Command (7)  |   | СОН          |   |              |             |          |           |   |  |  |

| C/D/H (6)    | 1 | LBA          | 1 | Drive        |             | Head (LE | 3A 27-24) |   |  |  |

| Cyl High (5) |   |              | C | ylinder High | n (LBA 23-1 | 6)       |           |   |  |  |

| Cyl Low (4)  |   |              | ( | Cylinder Lov | v (LBA 15-8 | 3)       |           |   |  |  |

| Sec Num (3)  |   |              | S | ector Numb   | ber (LBA 7- | 0)       |           |   |  |  |

| Sec Cnt (2)  |   | Sector Count |   |              |             |          |           |   |  |  |

| Feature (1)  |   |              |   | X            | K           |          |           |   |  |  |

The sectors indicated in the task file are left in erased states. This command is used in advanced of a write w/o erase or write multiple w/o erase command. Erased sectors return all zero data when read.

#### 5.1.4. Format Track-50H

Table 5-14. Format Track

| Bit ->       | 7 | 6                     | 5 | 4            | 3           | 2        | 1         | 0 |  |

|--------------|---|-----------------------|---|--------------|-------------|----------|-----------|---|--|

| Command (7)  |   |                       |   | 50           | θH          |          |           |   |  |

| C/D/H (6)    | 1 | LBA                   | 1 | Drive        |             | Head (LE | 3A 27-24) |   |  |

| Cyl High (5) |   |                       | C | ylinder Higł | ו (LBA 23-1 | 6)       |           |   |  |

| Cyl Low (4)  |   |                       | ( | Cylinder Lov | v (LBA 15-8 | 3)       |           |   |  |

| Sec Num (3)  |   |                       |   | X (LB/       | 47-0)       |          |           |   |  |

| Sec Cnt (2)  |   | Count (LBA mode only) |   |              |             |          |           |   |  |

| Feature (1)  |   |                       |   | >            | <           |          |           |   |  |

This command writes the desired head and cylinder of the selected drive with a vendor unique pattern. To remain host backward compatible, the drive expects a sector buffer of data from the host to follow the command with the same protocol as the Write Sector(s) command although the information in the buffer is not used by the drive. If LBA=1 then the number of sectors to format is taken from the Sec Cnt register (0=256).

# ➡ 5.1.5. Identify Drive-ECH

The Identify Drive command in Table 5-15 enables the host to receive parameter information from the drive. This command has the same protocol as the Read Sector(s) command. The parameter words in the buffer have the arrangement and meanings defined in Table 5-16. All reserved bits or words are zero. Table 5-16 is the definition for each field in the Identify Drive Information.

| Bit ->       | 7 | 6 | 5 | 4         | 3 | 2 | 1 | 0 |

|--------------|---|---|---|-----------|---|---|---|---|

| Command (7)  |   |   |   | EC        | Ή |   |   |   |

| C/D/H (6)    | Х | Х | Х | Drive     |   | > | < |   |

| Cyl High (5) |   |   |   | >         | < |   |   |   |

| Cyl Low (4)  |   |   |   | >         | < |   |   |   |

| Sec Num (3)  |   |   |   | >         | < |   |   |   |

| Sec Cnt (2)  |   |   |   | >         | < |   |   |   |

| Feature (1)  |   |   |   | $\rangle$ | < |   |   |   |

Table 5-15. Identify Drive

Table 5-16. Identify Drive Information

| Word<br>Address | Default<br>Value | Total<br>Bytes | Data Field Type Information                                                      |

|-----------------|------------------|----------------|----------------------------------------------------------------------------------|

| 0               | 044AH            | 2              | General configuration bit-significant information.                               |

| 1               | XXXXH            | 2              | Default number of cylinders; capacity dependent.                                 |

| 2               | 0000H            | 2              | Reserved.                                                                        |

| 3               | 00XXH            | 2              | Default number of heads; capacity dependent.                                     |

| 4               | 0000H            | 2              | Number of unformatted bytes per track.                                           |

| 5               | 0200H            | 2              | Number of unformatted bytes per sector.                                          |

| 6               | 00XXH            | 2              | Default number of sectors per track; capacity dependent.                         |

| 7-8             | XXXXH,XXXXH      | 4              | Number of sectors per drive (Word 7 = MSW, Word 8 = LSW);<br>capacity dependent. |

| 9               | 0000H            | 2              | Reserved.                                                                        |

| 10-19           | aaaa             | 20             | Serial number in ASCII (Right Justified).                                        |

| 20              | 0002H            | 2              | Buffer type (dual port).                                                         |

| 21              | 0001H            | 2              | Buffer size in 512 byte increments.                                              |

| 22              | 0004H            | 2              | Number of ECC bytes passed on Read/Write Long Commands.                          |

| 23-26           | aaaa             | 8              | Firmware revision in ASCII . Big Endian Byte Order in Word.                      |

| 27-46           | aaaa             | 40             | Model number in ASCII (Left Justified) Big Endian Byte Order in Word.            |

| 47              | 800XH            | 2              | Maximum number of sectors on Read/Write Multiple command; capacity dependent.    |

| Word<br>Address | Default<br>Value | Total<br>Bytes | Data Field Type Information                                                                                 |

|-----------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------|

| 48              | 0000H            | 2              | Double Word not supported.                                                                                  |

| 49              | 0F00H            | 2              | Capabilities: DMA Supported in True IDE mode (bit 8), LBA supported (bit 9).                                |

| 50              | 0000H            | 2              | Reserved.                                                                                                   |

| 51              | 0200H            | 2              | PIO data transfer cycle timing mode                                                                         |

| 52              | 0000H            | 2              | Single Word DMA data transfer cycle timing mode (not support-<br>ed).                                       |

| 53              | 0007H            | 2              | Data fields 54-58,64-70 and 88 are valid.                                                                   |

| 54              | XXXX             | 2              | Current numbers of cylinders.                                                                               |

| 55              | XXXX             | 2              | Current numbers of heads.                                                                                   |

| 56              | XXXX             | 2              | Current sectors per track.                                                                                  |

| 57-58           | XXXX             | 4              | Current capacity in sectors (LBAs) (Word 57 = LSW, Word 58 = MSW).                                          |

| 59              | 010XH            | 2              | Multiple sector setting is valid; low byte is capacity dependent.                                           |

| 60-61           | XXXX             | 4              | Total number of sectors addressable in LBA Mode.                                                            |

| 62              | 0000H            | 2              | Reserved                                                                                                    |

| 63              | 0X07H            | 2              | Multiword DMA modes 0-2 are supported; upper byte reflects currently selected MWDMA mode.                   |

| 64              | 0003H            | 2              | Advanced PIO modes supported (modes 3 and 4)                                                                |

| 65              | 0078H            | 2              | Minimum MWDMA cycle time per word is 120ns.                                                                 |

| 66              | 0078H            | 2              | Recommended MWDMA cycle time is 120ns.                                                                      |

| 67              | 0078H            | 2              | Minimum PIO cycle time without IORDY flow control is 120ns.                                                 |

| 68              | 0078H            | 2              | Minimum PIO cycle time with IORDY flow control is 120ns.                                                    |

| 69-79           | -                | 22             | Reserved                                                                                                    |

| 80              | 0020H            | 2              | Supports ATA5 standard.                                                                                     |

| 81              | 0000H            | 2              | No minor revision reported.                                                                                 |

| 82              | 3008H            | 2              | Read/Write Buffer command supported; PACKET Command,<br>Security Mode and SMART feature sets not supported; |

| 83              | 7000H            | 2              | 48-bit mode not supported; CFA feature set not supported.                                                   |

| 84              | 4000H            | 2              | Features defined in this word not supported.                                                                |

| 85              | 3008H            | 2              | Read/Write Buffer and Power Management features enabled.                                                    |

| 86              | 4000H            | 2              | CFA Feature set not enabled.                                                                                |

| 87              | 4000H            | 2              | Features defined by this word not enabled.                                                                  |

| 88              | XX1FH            | 2              | UDMA Modes 0-4 supported.                                                                                   |

| 89-99           | 0000H            | 22             | Reserved                                                                                                    |

| 100-103         | XXXXH            | 8              | Maximum user LBA for 48-bit addressing mode (not used).                                                     |

| 104-255         | -                |                | Reserved                                                                                                    |

#### 오 5.1.6. Idle-97H, E3H

These commands are treated as NOPs by the drive. Since the drive goes into sleep mode after every command, these extra IDLE commands are redundant.

Table 5-17. Idle

| Bit ->       | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |

|--------------|---|---|---|-------|--------|---|---|---|

| Command (7)  |   |   |   | E3H o | or 97H |   |   |   |

| C/D/H (6)    |   | Х |   | Drive |        | > | < |   |

| Cyl High (5) |   |   |   | >     | <      |   |   |   |

| Cyl Low (4)  |   |   |   | >     | <      |   |   |   |

| Sec Num (3)  |   |   |   | >     | <      |   |   |   |

| Sec Cnt (2)  |   |   |   | >     | <      |   |   |   |

| Feature (1)  |   |   |   | >     | <      |   |   |   |

#### 5.1.7. Idle Immediate-95H, E1H

Table 5-18. Idle Immediate

| Bit ->       | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |

|--------------|---|---|---|-------|--------|---|---|---|

| Command (7)  |   |   |   | E1H o | or 95H |   |   |   |

| C/D/H (6)    |   | Х |   | Drive |        | > | < |   |

| Cyl High (5) |   |   |   | >     | <      |   |   |   |

| Cyl Low (4)  |   |   |   | >     | <      |   |   |   |

| Sec Num (3)  |   |   |   | >     | <      |   |   |   |

| Sec Cnt (2)  |   |   |   | >     | <      |   |   |   |

| Feature (1)  |   |   |   | >     | <      |   |   |   |

#### 5.1.8. Initialize Drive Parameters-91H

The Initialize Drive Parameters command in Table 5-19 causes the drive to set BSY, enter the Idle (Read) mode, clear BSY and generate an interrupt. This command enables the host to set the number of sectors per track and the number of heads per cylinder. Only the Sector Count and the Drive/Drive/Head registers are used by this command. This command is obsolete in ATA5 but is supported for backwards compatibility.

| Bit ->       | 7 | 6                 | 5 | 4     | 3  | 2          | 1           | 0   |  |

|--------------|---|-------------------|---|-------|----|------------|-------------|-----|--|

| Command (7)  |   |                   |   | 91    | Н  |            |             |     |  |

| C/D/H (6)    | Х | 0                 | Х | Drive | Ma | ax Head (n | o. of heads | -1) |  |

| Cyl High (5) |   |                   |   | >     | <  |            |             |     |  |

| Cyl Low (4)  |   |                   |   | >     | <  |            |             |     |  |

| Sec Num (3)  |   |                   |   | >     | <  |            |             |     |  |

| Sec Cnt (2)  |   | Number of Sectors |   |       |    |            |             |     |  |

| Feature (1)  |   |                   |   | >     | <  |            |             |     |  |

Table 5-19. Initialize Drive Parameters

# 5.1.9. Read Buffer-E4H

The Read Buffer command in Table 5-20 enables the host to read the current contents of the SSD's sector buffer. This command has the same protocol as the Read Sector(s) command.

| Bit ->       | 7 | 6 | 5 | 4     | 3  | 2 | 1 | 0 |

|--------------|---|---|---|-------|----|---|---|---|

| Command (7)  |   |   |   | E4    | 4H |   |   |   |

| C/D/H (6)    |   | Х |   | Drive |    | 2 | X |   |

| Cyl High (5) |   |   |   | )     | X  |   |   |   |

| Cyl Low (4)  |   |   |   | >     | X  |   |   |   |

| Sec Num (3)  |   |   |   | >     | X  |   |   |   |

| Sec Cnt (2)  |   |   |   | >     | X  |   |   |   |

| Feature (1)  |   |   |   | >     | X  |   |   |   |

Table 5-20. Read Buffer

#### • 5.1.10. Read Multiple-C4H

The Read Multiple command in Table 5-21 performs similarly to the Read Sectors command. Interrupts are not generated on every sector, but on the transfer of a block, which contains the number of sectors defined by a Set Multiple, command.

| Bit ->       | 7 | 6                         | 5 | 4            | 3           | 2        | 1         | 0 |  |  |

|--------------|---|---------------------------|---|--------------|-------------|----------|-----------|---|--|--|

| Command (7)  |   | C4H                       |   |              |             |          |           |   |  |  |

| C/D/H (6)    | 1 | LBA                       | 1 | Drive        |             | Head (LE | 3A 27-24) |   |  |  |

| Cyl High (5) |   | Cylinder High (LBA 23-16) |   |              |             |          |           |   |  |  |

| Cyl Low (4)  |   |                           | ( | Cylinder Lov | v (LBA 15-8 | 3)       |           |   |  |  |

| Sec Num (3)  |   |                           | S | ector Num    | ber (LBA 7- | 0)       |           |   |  |  |

| Sec Cnt (2)  |   | Sector Count              |   |              |             |          |           |   |  |  |

| Feature (1)  |   |                           |   | >            | <           |          |           |   |  |  |

Table 5-21. Read Multiple

Command execution is identical to the Read Sectors operation except that the number of sectors defined by a Set Multiple command is transferred without intervening interrupts. DRQ qualification of the transfer is required only at the start of the data block, not on each sector.

The block count of sectors to be transferred without intervening interrupts is programmed by the Set Multiple Mode command, which must be executed prior to the Read Multiple command. When the Read Multiple command is issued, the Sector Count Register contains the number of sectors (not the number of blocks or the block count) requested. If the number of requested sectors is not evenly divisible by the block count, as many full blocks as possible are transferred, followed by a final, partial block transfer. The partial block transfer is for n sectors, where:

n = (sector count)—module (block count).